Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по делопроизводству

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Рефераты по косметологии

Рефераты по криминалистике

Рефераты по криминологии

Рефераты по науке и технике

Рефераты по кулинарии

Рефераты по культурологии

Рефераты по зарубежной литературе

Рефераты по логике

Рефераты по логистике

Рефераты по маркетингу

Рефераты по международному публичному праву

Рефераты по международному частному праву

Рефераты по международным отношениям

Рефераты по культуре и искусству

Рефераты по менеджменту

Рефераты по металлургии

Рефераты по муниципальному праву

Рефераты по налогообложению

Рефераты по оккультизму и уфологии

Рефераты по педагогике

Рефераты по политологии

Рефераты по праву

Биографии

Рефераты по предпринимательству

Рефераты по психологии

Рефераты по радиоэлектронике

Рефераты по риторике

Рефераты по социологии

Рефераты по статистике

Рефераты по страхованию

Рефераты по строительству

Рефераты по схемотехнике

Рефераты по таможенной системе

Сочинения по литературе и русскому языку

Рефераты по теории государства и права

Рефераты по теории организации

Рефераты по теплотехнике

Рефераты по технологии

Рефераты по товароведению

Рефераты по транспорту

Рефераты по трудовому праву

Рефераты по туризму

Рефераты по уголовному праву и процессу

Рефераты по управлению

Реферат: Розробка мікропроцесорного пристрою системи автоматичного регулювання

Реферат: Розробка мікропроцесорного пристрою системи автоматичного регулювання

Міністерство освіти України

Державний

університет

“Львівська

політехніка”

Комп’ютерний факультет

Кафедра систем автоматизованого проектування

ПОЯСНЮВАЛЬНА ЗАПИСКА

до курсової роботи

з дисципліни

“Електронні

обчислювальні

машини

і

мікропроцесорні

системи”

на

тему: Розробка

мікропроцесорного

пристрою

системи

автоматичного

регулювання

|

Допущено до захисту: Дата: |

Виконав: студентка групи ІСМ-41 Шаховська Н. Б. Прийняв: Теслюк В. М. Оцінка: Залікова книжка № 9517007 Дата: |

Львів

1998

Державний

університет

“Львівська

політехніка”

Кафедра САП

Дисципліна “Електронні обчислювальні машини і мікропроцесорні системи”

Спеціальність “Інформаційні системи та мережі”

Курс IV Група ІСМ-41 Семестр 7

Завдання

на курсову роботу студента

Шаховської Н. Б.

1. Тема проекту: “Розробка мікропроцесорного пристрою системи автоматичного регулювання ”

2. Термін здачі проекту: 16.12.1998

3. Вихідні дані для проекту.

Останні цифри залікової книги: mn=07. За формулою

![]()

визначаємо

k=18 l=8; рівняння

–

![]()

k=3 l=1; розрядність АЦП – 8;

k=2 l=1; вхідний сигнал – однополярний невід’ємний;

k=9 l=8; організація обміну з АЦП – через переривання RST 7;

k=7 l=2; вид функціонального вузла – системний контролер з використанням КР580ВК28.

4. Зміст розрахунково-пояснювальної записки:

1) Для заданого рівняння систем в регулювання здійснити йoгo часткову дискретизацію і отримати відповідне рівняння цифрового фільтра (ЦФ). Побудувати аналогову схему, яка описується заданим рівнянням.

2) Скласти і детально описати структурну схему МПП з врахуванням особливостей індивідуального завдання.

3) Скласти схему алгоритму функціонування МПП. Вибрати структуру представлення даних при заданій розрядності АЦП, який здійснює дискретизацію і квантування вхідного сигналу.

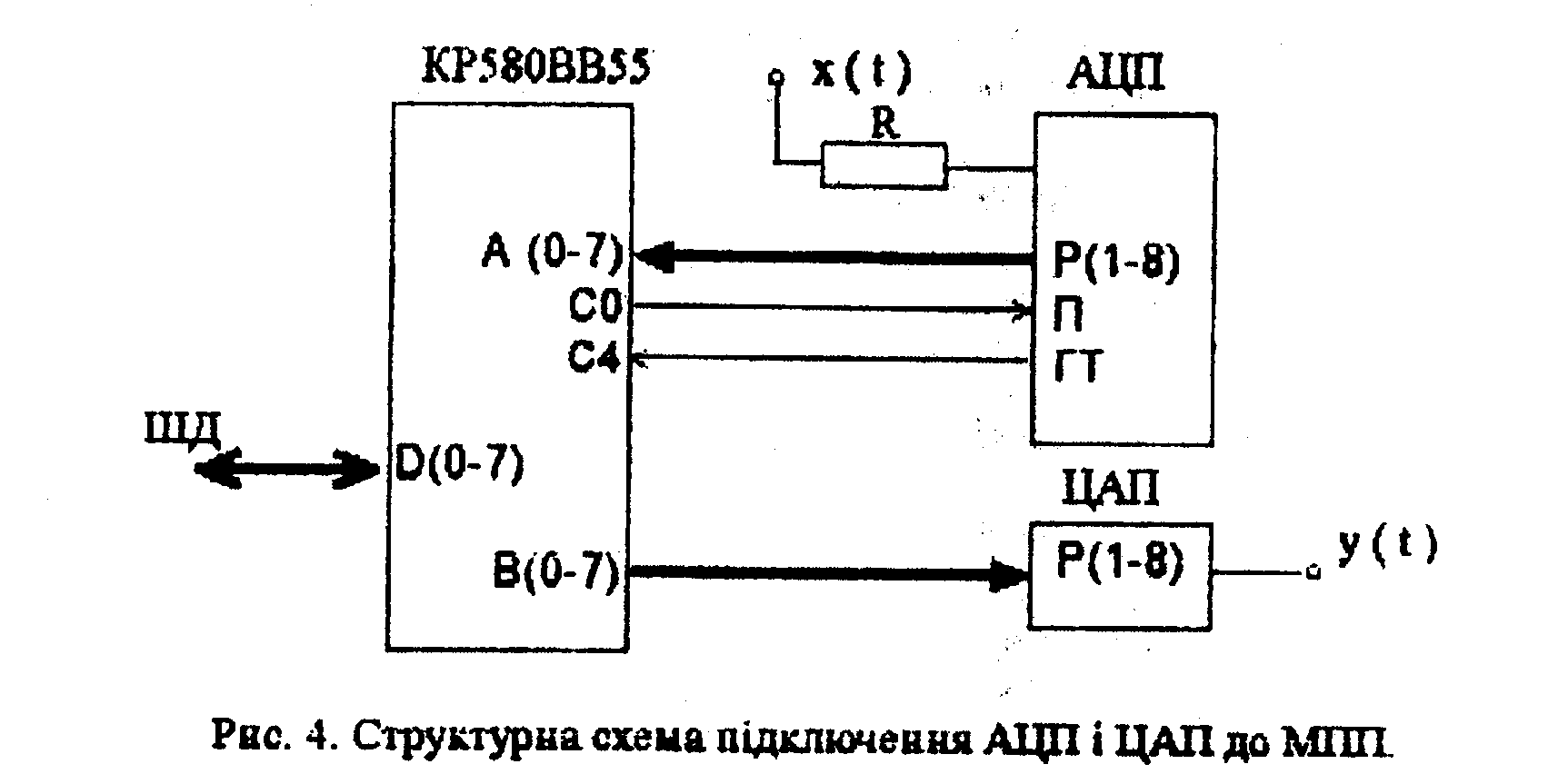

4) У відповідності з індивідуальним завданням вибрати типи АЦП і ЦАП. Скласти і описати принципові схеми підключення АЦП і ЦАП до МПП. Нарисувати часову діаграму роботи АЦП.

5) Скласти на мові асемблеру мікропроцесора КР580ВМ80 програму вводу інформації через АЦП і виводу через ЦАП.

6) Скласти програму відповідної цифрової обробки інформації. Оцінити верхню граничну частоту ЦФ.

7) Скласти і детально описати фрагмент принципової схеми реалізації функціонального вузла, вказаного в індивідуальному завданні.

5. Перелік графічного матеріалу

Принципова схема електрична МПП

6. Дата видачі: 15.9.1998

Календарний план

|

№ п/п |

Назва етапів курсового проекту |

Термін виконання етапів проекту |

Примітки |

|

1 |

Побудова рівняння цифрового фільтру |

16.09 – 18.09 |

|

|

2 |

Побудова схеми реалізації ЦФ |

19.09 – 20.09 |

|

|

3 |

Побудова аналогової схеми ЦФ |

22.09 – 28.09 |

|

|

4 |

Визначення структури МПС |

30.10 – 02.10 |

|

|

5 |

Розробка алгоритму функціонування ЦФ |

05.09 – 10.10 |

|

|

6 |

Визначення структури представлення даних |

11.10 – 12.10 |

|

|

7 |

Вибів АЦП |

13.10 – 16.10 |

|

|

8 |

Побудова схеми підключення АЦП |

17.10 – 19.10 |

|

|

9 |

Вибір ЦАП |

20.10 – 21.10 |

|

|

10 |

Побудова схеми підключення ЦАП |

22.10 – 25.10 |

|

|

11 |

Розробка програми переривань |

01.11 – 02.11 |

|

|

12 |

Розробка основної програми |

05.11 – 10.11 |

|

|

13 |

Визначення верхньої граничної частоти ЦФ |

13.11 – 15.11 |

|

|

14 |

Побудова принципової схеми електричної ЦФ |

20.11 –27.11 |

|

|

15 |

Опис принципової схеми СК |

27.11 – 30.11 |

|

|

16 |

Написання та оформлення пояснювальної записки |

02.12 – 06.12 |

Анотація

Виконання даної курсової роботи присвячене розробці мікропроцесорних пристроїв систем автоматизованого проектуваня. Загальний обсяг роботи становить 40 сторінки. В даній курсовій роботі є 14 рисунків та 5 таблиць. Для виконання роботи викоритано 9 літературних джерел плюс методичка по оформленню курсової роботи. За своєю структурою вона ділиться на 7 частин, кожна з яких відповідає певному завданню, що перераховані вище.

Виконання курсової роботи присвячене для реалізації наступної мети:

поглиблення теоретичних знань, технічних і програмних засобів мікропроцесорних пристроїв;

розвиток навиків самостійної розробки загальної структури МПП з аналогово-цифровим і цифро-анлоговим перетворенням інформації, побудови принципових схем окремих вузлів принципів, розробки та відлагодження програмного забезпечення на мові асамблеру мікропроцесора КР580ВМ;

набуття навиків роботи з технічною та довідниковою літературою з питань реалізації ряду вузлів МПП, вибору аналого-цифрового і цифро-аналогово перетворювачів (АЦП і ЦАП), використання стандартних підпрограм з прикладного програмного забезпечення МП КР580ВМ80.

ЗМІСТ

Державний

університет

“Львівська

політехніка” 2

Анотація 4

ЗМІСТ 5

специфікації 6

ВСТУП 7

1. ПОБУДОВА ЦИФРОВОГО ФІЛЬТРА 9

1.1 Побудова аналогової схеми 10

2. Структурна схема МП-пристрою 13

3. Алгоритм функціонування МП-пристрою 15

3.1

Схема алгоритму

функціонування

МПП

як цифрового

фільтру, що

визначається

заданим рівнянням 15

3.2 Вибір структури представлення даних 18

4. Вибір АЦП і ЦАП 20

4.1 Вибір АЦП 20

4.2 Вибір ЦАП 25

5.

Програма вводу

інформації

через АЦП і

виводу через

ЦАП 28

6. Програма цифрової обробки інформації. 30

Основна програма: 31

6.1 Оцінка верхньої граничної частоти фільтру 32

7.

Опис фрагменту

принципової

схеми

реалізації

системного

контролера. 33

висновок 38

Список літератури 39

додатки 40

специфікації

|

Абревіатура |

Значення |

|

АЦП БЕ ВІС ГТІ ДШВ/В ДШП ДОН ЗП КН МК МП МПП МПС ОЗП ПЗП ПІ ПП ППІ РКС РПН СК СШ ТГ ША ШД ШК ШФ ЦАП ЦП ЦФ |

- аналогово-цифровий перетворювач - буферний елемент - велика інтегральна схема - генератор тактових імпульсів (див. ТГ) - дешифратор каналів вводу/виводу - дешифратор адрес пам’яті - джерело опорної напруги - запам’ятовуючий пристрій - компаратор напруги - мікроконтролер - мікропроцесор - мікропроцесорний пристрій - мікропроцесорна система - оперативний запам’ятовуючий пристрій - постійний запам’ятовуючий пристрій - підсилювач-інвертор - підпрограма - паралельний програмований інтерфейс - регістр керуючого слова - регістр послідовних наближень - системний контролер - системна шина - тактовий генератор (див. ГТІ) - шина адрес - шина даних - шина керування - шифратор - цифро-аналоговий перетворювач - центральний процесор - цифровий фільтр |

ВСТУП

Термін “мікропроцесор”, звичайно, несе певну інформацію про пристрій, названий таким іменем. Це пристрій для обробки даних.

На відміну від стандартного ЦП логічні схеми МП реалізовані на одній або декілька ВІС, а так як останній також називаються мікросхемами, то стає зрозумілим походження терміна “мікропроцесор”.

Очевидно, що обробка даних – одна із головних функцій МП, яка включає як і маніпулювання так і обрахунок даних. Іншою функцією МП є управління системою. Схеми управління дозволяють декодувати і виконувати програми – набір команд для обробки даних. Робота мікропроцесора складається з наступних кроків: спочатку вибирається команда, потім логічна схема її декодує, після чого здійснюється виконання цієї команди. Також відбувається обмін інформацією з зовнішніми пристроями, які під’єднані до мікропроцесора.

Мікропроцесори являють собою цифрові великі інтегральні схеми (ВІС), призначені для виконання простих операцій, інакше названих командами, що зчитуються і здійснюються послідовно з великою швидкістю. До числа внутрішніх схем мікропроцесора відносяться багаторозрядні регістри, рівнобіжні тракти даних, буфери для підключення зовнішніх пристроїв, багатофункціональні схеми, логічні схеми синхронізації і керування. Багатофункціональні схеми придназначені для реалізації простих арифметичних і логічних дій над двійковими числами, що знаходяться в регістрах процесора, і пересилок даних як усередині процесора, так і між ним і зовнішніми пристроями. Схеми синхронізації і керування задають порядок дій процесора, для виконання функцій синхронізації їм необхідні тактові імпульси, що постійно поступають.

Розвиток інтегральної технології і схемотехніки цифрових електронних схем призвів до появи інтегральних мікросхем із великою і дуже великою ступенями інтеграції (ВІС і ДВІС), що містять на однім кристалі (в однім корпусі) декілька десятків тисяч, а в останніх розробках сотні тисяч елементарних транзисторів. На основі таких схем в останні роки вдалося створити мікропроцесори функціонально закінчені, що управляються збереженою в пам'яті програмою (здебільшого малорозрядні) пристрої опрацювання цифрової інформації, виконані у виді однієї або декількох ВІС або ДВІС.

Мікропроцесорні засоби використовуються у виді мікропроцесорних комплектів інтегральних мікросхем, що мають єдине конструктивно-технологічне виконання і призначених для спільного застосування. Мікропроцесорний комплект крім самого мікропроцесора містить мікросхеми, що підтримують функціонування мікропроцесора і розширюють його логічні можливості.

Мікроконтролер являє собою логічний автомат з високим ступенем детермінованості, який допускає небагато варіантів в його системному включенні.

В пристроях управління об’єктами мікроконтролери розглядаються у вигляді сукупності апаратно-програмних засобів. При проектуванні мікроконтролерів треба вирішувати одну з найскладніших задач розробки: задачу оптимального розподілу функцій між апаратними засобами і програмним забезпеченням. Рішення такої задачі ускладнюється тим, що взаємоз’язок і взаємодія між апаратними і програмними засобами динамічно змінюються.

В даний час розповсюджена така методологія, при якій весь цикл розробки мікроконтролера поділяють на три фази:

1) аналіз задачі і вибір апратних засобів;

2) розробка прикладного програмного забезпечення;

3) комплексування апаратних засобів і програмного забезпечення;

Цифро-аналоговим перетворювачем (ЦАП) називають пристрій, що генерують вихідну аналогову величину, яка відповідає цифровому коду, що поступає на вхід перетворювача. Цифро-аналогові перетворювачі використовуються для узгодження ЕОМ з аналоговими пристроями.

Дана курсова робота присвячена розробці ЦФ по заданому рівнянню. Її виконання поділено на етапи, кожен з яких висвітлює ту частину реалізації, яка описується.

1. ПОБУДОВА ЦИФРОВОГО ФІЛЬТРА

Кожний

неперервний

сигнал, що

представляється

змінною в часі

напругою,

характеризується

своїм спектром

частот. Будь-яка

частота або

полоса частот

може бути посилена,

послаблена,

виключена або

виділена фільтрацією.

Фільтрація

– це процес

зміни спектра

частот сигнала.

Прикладом

фільтрації

сигналів може

служити виключення

шумів, визваних

недосконалістю

каналів передачі,

розділення

двох або більше

сигналів, спеціально

змішаних для

збільшення

пропускної

здатності

канала зв’язку,

демодуляція

сигналів. Будь-який

неперервний

сигнал, спектр

якого обмежений

верхніми частотами,

може бути

представлений

у вигляді

послідовності

своїх значень,

що розділені

один від одного

проміжками

часу

![]() .

.

Цифровий фільтр – пристрій, який дозволяє перетворити дискретизований сигнал x(t) у інший y(t). Це цифрова схема для зміни частотного спектра дискретних сигналів. Цифровий фільтр може бути реалізований як апаратурно, так і програмно. При апаратурній реалізації необхідними схемними елементами є перемножувачі, суматори і елементи затримки [1].

Задано

рівняння

автоматичного

регулювання

вхідного x(t) та

вихідного y(t)

сигналів:![]() (1.1).

(1.1).

У даному

рівнянні x(t) –

вхідний сигнал,

який є відхиленням

від еталонного

сигналу, y(t) –

керуючий сигнал,

який подається

з системи регулювання

на об’єкт керування,

![]() – стала часу,

– стала часу,

![]() – частота.

– частота.

Дискретизація

аналогового

рівняння полягає

в заміні безперервної

величини її

дискретними

відліками

![]() (1.2) і відповідними

перетвореннями

похідних.

(1.2) і відповідними

перетвореннями

похідних.

Дискретизація

першої похідної:

![]() (1.3).

(1.3).

Дискретизація

другої похідної:

![]() (1.4).

(1.4).

Звідси

випливає:

![]() .(1.5).

.(1.5).

Спростимо вираз:

![]() (1.6)

(1.6)

Здійснимо заміну:

,

,

![]() ,

,

![]() (1.7).

(1.7).

Тоді:![]() (1.8)

(1.8)

при

(1.9).

(1.9).

Дане рівняння є рекурсивним фільтром, оскільки присутні члени yn-1 та yn-2.

Звідси, структурна схема реалізації цифрового фільтру зображена на рис.1.1.

Рис 1.1 Структурна схема реалізації цифрового фільтра;

ХУ – елементи

множення, DL –

елементи затримки,

![]() – суматор.

– суматор.

Недоліками цифрових фільтрів, які реалізовані на основі МП (наприклад, серія КР580, яка використовується), є обмежена швидкодія.

1.1 Побудова аналогової схеми

При побудові аналогової схеми, яка відповідає заданому пропорційно-диференційному рівнянню (1.8)

використовуємо перетворення Лапласа [9]:

(1.10)

(1.10)

Коефіцієнт при х(р) має вид дробово-раціонального виразу, в якому знаменник є сумою зображень за Лапласом опорів резистора, конденсатора та індуктивності ( в залежності від порядку заданого рівняння), а чисельник є частиною цієї суми. Вид цього дробово-раціонального виразу визначає аналогову схему.

Підставимо у рівняння перетворення Лапласа:

![]() (1.11)

(1.11)

Отримане алгебраїчне рівняння розв’яжемо відносно у(р):

. (1.12)

. (1.12)

Домножимо

чисельник і

знаменник на

![]() .

Отримаємо:

.

Отримаємо:

(1.13).

(1.13).

А це еквівалентно рівнянню Г-подібного фільтра з Г-подібним входом з рівнянням

![]() (1.14)

(1.14)

із відомою схемою (рис. 1.2):

рис. 1.2 Схема Г-подібного фільтру з Г-подібним входом

В отриманому нами виразі знаменник являє собою опір послідовного коливального кола з втратами, а чисельник є опором конденсатора, тобто аналогова схема являє собою послідовне з’єднання резистора, індуктивності та ємності, причому вихідна напруга знімається з конденсатора.

Тому Z1 = ZR+ ZL; Z2= ZC (1.15),

де

![]() (1.16).

(1.16).

Тут k – довільна стала.

Т

обто

схема реалізації

даного фільтру

має такий вигляд:

рис. 1.3 Аналогова схема, яка описується заданим рівнянням

2. Структурна схема МП-пристрою

Мікропроцесорний пристій – функціонально і конструктивно закінчений пристрій, який представляє собою схемно-конструктивне з’єднання декількох схем, який включає один або декілька мікропроцесорів, призначений для отримання, обробки, передачі, перетворення та керування інформацією.

Для мікропроцесорних пристроїв характерна шинна структура, під якою розуміється те, що всі компоненти МП - пристрою під’єднані до так званої системної шини – набору ліній, що з’єднують елементи системи [1].

Структурна схема можливої реалізації проектованого МП-пристрою наступна (рис. 2.1).

рис. 2.1 Структурна схема МПП

де:

МП – мікропроцесор;

ПЗП – постійний запам’ятовуючий пристрій;

ТГ – тактовий генератор;

ОЗП – оперативний запам’ятовуючий пристрій;

СК – системний контролер;

АЦП – аналого-цифровий перетворювач;

ЦАП – цифро - аналоговий перетворювач;

ДШП – дешифратор адрес пам’яті;

ДШВ/В – дешифратор адрес вводу/виводу.

Системна шина розділяється на три окремі шини:

ШД – шина даних;

ША – шина адрес;

ШК – шина керування.

Лінії системної шини характеризується спрямованістю (тобто хто з пристроїв є визначальним за рівнем сигналу). Тут ШД – двоспрямована; ША – односпрямована; ШК – набір окремих ліній, що мають свій напрям. За рахунок того, що виводи всіх компонент МП - пристрою під’єднані до СШ, вони повинні мати крім станів, що забезпечують логічний 0 чи 1 на виході третій стан, стан з високим вихідним опором.

Опишемо складові МПС.

Мікропроцесор в складі МП-пристрою виконує функції:

формує адреси команд,

видає команди з пам’яті,

їх дешифрує,

видає для них команди потрібні адреси, виконує над ними опереції – передбачені команди, при неодхідності записує результат в пам’ять,

формує керуючі сигнали для обміну, реагує на можливі зовнішні сигнали.

Тактовий генератор призначений для формування синхроімпульсів для роботи МП і інших пристроїв МП. Синхроімпульси мають амплітуду 12B, але відрізняються один від одного щільністю і є зсунуті. Крім того мікросхема КР580ГФ24, яка виконує функцію ТГ, приймає участь в прийомі та видачі керучих сигналів СШ.

ПЗП служить для постійного зберігання потрібних даних і програм. У випадку даного цифрового фільтру він зберігає програму, за якою працює цифровий фільтр, а також постійні коефіціенти.

ОЗП служить для тимчасового зберігання інформації, потрібної для розрахунків.

СК виконує 3 функції:

фіксація слова стану процесора;

формування частини сигналів, які належать шині керування МПС;

буферизація шини даних.

Він формує керуючі сигнали по сигналам стану МП при зверненні до ЗП: RD i WR, при зверненні до ПВВ: RDIO, WRIO, INTA. А також забезпечує прийом і передачу 8-розрядної інформації між каналом данихМП по виходам D7 – D0 і системним каналом по DB7–DB0. Він складається з двонаправленої буферної схеми даних, регістрів стану і дешифраторів керуючих сигналів.

ППІ в даному МП-пристрої служить для обміну інформацією між МП і зовнішніми пристроями АЦП і ЦАП. Крім того, в склад МП-пристрою входять такі допоміжні елементи, як буферний регістр для організації переривань RST 7, окремі логічні елементи, дешифратори.

3. Алгоритм функціонування МП-пристрою

3.1 Схема

алгоритму

функціонування

МПП

як цифрового

фільтру, що

визначається

заданим

рівнянням

Система переривань призначена для прийому, пріоритетноі обробки і обслуговування запитів переривань. В загальному випадку запити переривань можуть формуватися по командах програми, внутрішніх або зовнішніх джерелах. Прийом і обробку програмних і внутрішніх переривань виконують внутрішні засоби процесора. При проектуванні системи для обробки цих переривань необхідно розробити програми обробки переривань.

Реалізація

переривання

виконується

за допомогою

команди

RST N. Джерела

запитів переривань

ідентифікуються

двома способами:

послідовне опитування;

векторний спосіб.

Адреси команд JМР INТ І у таблиці переходів для кожного запиту переривань визначаються на основі коду, що ідентифікує запит, ККК у командах RSТ N або САLL ADRК, що формуються джерелом запиту переривання. По команді RSТ N адреси в таблиці переходів приймають значення 0000 000, 00 КК, К 000. Таким чином, таблицю переходів розташовують з адреси 000016 по адресу 003F16 з інтервалом у 8 адрес. При використанні команди САLL ADRV адреси в таблиці переходів задаються безпосередньо адресною частиною команди САLL, тому таблиця може розташовуватися в довільному місці ЗП. Для формування команд RSТ N або САLL ADRV V необходими зовнішнього засоби, сопрягаемие з МП через системну шину [3].

Для прийому запитів переривання і формування сигналу переривання МП потребує лише регістр запитів переривань із буфером системної шини і схеми логічного об'єднання вхідних запитів переривань. Програма опитування зчитує вміст регістра запитів переривань, опитує кожен його розряд і передає керування програмам обслуговування переривань.

Такий засіб побудови системи переривань доцільний при невеличкому числі обслуговуючих запитів переривань, тому що засіб опитуванння при великому числі запитів потребує значних витрат часу в порівнянні з векторним.

Для реалізації цифрового фільтру з функціональною залежністю (1.1):

![]() (3.1)

(3.1)

якe в результаті дискретизації набрало вигляду (1.8):

![]() (3.2)

(3.2)

з вводом значень xn через переривання з RST N може бути запропонований наведений нижче алгортм.

Рис 3.1 Алгоритм функціонування МП – пристрою

Рис 3.2 Алгоритм для програми обробки переривань

В процесі обробки запиту на переривання (яке здійснюється подачею на вхід INT мікропроцесора логічної 1) мікропроцесор сигналом INTE=0 забороняє (ігнорує) всі можливі запити та переривання від інших пристроїв ( для даного цифрового фільтру). Запит на переривання може бути тільки від одного пристрою і виконується машинний цикл переривання, в якому виробляється керуюче слово з одиницями в INTA (підтвердженя переривання), MI (початок машинного циклу). W0 (запис або вивід), а MEMR=0 (читання з пам’яті). При цьому сигнал DBIN=1 (прийом інформації з ШД). Тобто МП читає з ШД деяку інформацію, яка не видається, а вибирається з пам’яті чи портів. В цей момент на ШД повинен бути код команди RST N (для даного завдання RST 7):

|

11ККК111 |

Для RST 7 код буде 111111111. Ця команда здійснює перехід на адресу 8*N. Для RST7 це дорівнює: 8*N=8*7=5610=38H=00111000В.

У процесорах, побудованих на основі ВІС КР580ВК28 (КР580ВК38), можна формувати команду RST 7 (11111111) шляхом підключення виходу підтвердження переривання INТА ВІС до джерела +12В, що дозволяє звертатися до таблиці переходів за адресою 3816, по якій розміщають програму ідентифікації запитів від декількох джерел опитуванння.

При переході на дану адресу в стек записується адреса повернення.

Необхідність в команді EI (дозвіл переривань) зумовлена тим, що вихід INTE в стан логічної 1 (дозвіл переривань) можна перевести тільки програмним способом, а в стан логічного 0 його можна встановити, як програмною командою DI, так і апаратним способом.

3.2 Вибір структури представлення даних

Структура представлення даних, які входять в рівняння цифрового фільтру, визначається виходом рівняння і розрядністю АЦП. При заданій розрядності АЦП – 8 розрядів та вхідним додатнім однополярним сигналом, для представлення xn потрібно 8 розрядів, тобто xn повинний виражатись однобайтовим словом. Виходячи з цього, знайдемо, скільки розрядів займатиме результат yn та yn-1 .

Для заданого рівняння (дискретизованого) цифрового фільтру у вигляді:

![]()

коефіцієнти

визначаються: (3.3);

(3.3);

![]() (3.4)

(3.4)

![]() (3.5).

(3.5).

Припустимо,

що для констант

![]() відведемо по

три біта на

кожну. Їх максимальне

значення при

цьому (найгірший

варіант) буде

дорівнювати

7. Звідси, посилаючись

на (3.3) – (3.5), а0=0,4969,

b0=0,50020, c0=-0,006134. Мінімальне

дробове число

в двійковій

формі, яке може

розміститись

у восьми розрядах

– 2-810=0,00290625. Як

бачимо, всі

коефіцієнти

більші цього

числа, але менші

за одиницю.

Візьмемо для

їх представлення

один байт (на

кожного).

відведемо по

три біта на

кожну. Їх максимальне

значення при

цьому (найгірший

варіант) буде

дорівнювати

7. Звідси, посилаючись

на (3.3) – (3.5), а0=0,4969,

b0=0,50020, c0=-0,006134. Мінімальне

дробове число

в двійковій

формі, яке може

розміститись

у восьми розрядах

– 2-810=0,00290625. Як

бачимо, всі

коефіцієнти

більші цього

числа, але менші

за одиницю.

Візьмемо для

їх представлення

один байт (на

кожного).

Тепер знайдемо, скільки розрядів потрібно для представлення yn та уn-1.

Так як вхідний сигнал однополярний, то нам не потрібно відводити розряд під знак.

Розрядність

добутків а0хn,

b0yn, c0yn-1 не

буде перевищувати

8 біт, так як

коефіцієнти

а0, b0, c0 є менші

по модулю за

одиницю. Їх

сума теж не

перевищує 255,

так як

![]() ,

а с0 менше нуля

.Тоді розрядність

yn буде дорівнювати

розрядності

xn, тобто 8 біт.

,

а с0 менше нуля

.Тоді розрядність

yn буде дорівнювати

розрядності

xn, тобто 8 біт.

Як було вже визначено, структура представлення даних буде наступною: а0, b0, c0 – числа з фіксованою десятковою крапкою перед старшим розрядом, yn ,yn-1 та yn-2 – цілі числа з фіксованою десятковою крапкою після молодшого розряду з розрядністю 1 байт, хn – ціле число з фіксованою десятковою крапкою після молодшого розряду з розрядністю 1 байт.

хn

|

|

a0

b0

|

1 байт |

c![]()

![]() 0

0

yn

yn-1

yn-2

|

|

Рис 3.3 Структура представлення даних в МПП

Дані

представлятимуться

у вигляді масиву

в оперативній

пам’яті. Після

обчислення

величина yn

заміщує величину

yn-1, yn-1

– величину

yn-2,

а значення xn

вводиться від

АЦП. Адреса

таблиці – 500H. Числа

розміщені у

порядку наростання

значення адреси.

4. Вибір АЦП і ЦАП

У відповідності з критеріями даної роботи розрядність АЦП має бути 8 біт, а ЦАП із визначеного вище – 8 біт. Критерієм вибору АЦП і ЦАП (крім розрядності) можуть бути наступні параметри:

час перетворення – визначається інтервалом часу від моменту досягнення вихідного сигналу до моменту подачі цифрового сигналу до моменту досягнення вихідним сигналом встановленого значення;

похибка перетворення – найбільше значення відхилення значення аналогового сигналу від розрахункового;

нелінійність – максимальне відхилення лінійно наростаючої напруги від прямої лінії, яка з’єднуєточку нуля і максимального вихідного сигналу.

4.1 Вибір АЦП

Перетворення аналогового сигналу в цифровий здійснюється за допомогою АЦП і представляє собою вимірювальний процес, який полягає в порівнянні аналогового сигналу з еталонною напругою, значення якої відомо наперед з великою точністю. В результаті цього непнрервне значення сигналу замінюється найближчим еталонним значення напруги, іншими словами, відбувається процес квантування по рівню.

Відомості про АЦП, які можуть бути використані в даній курсовій роботі, зведені в таблиці 4.1:

Таблиця 4.1

|

Мікросхема |

Вид перетвореня |

Час

пере t, мкс |

К-ть вихо-дів |

Похиб |

Диф. неліній-ність, % |

Абс. похибка перетво-рень, % |

Розрядність |

|

К572ПВ3 К1107ПВ4 К1107ПВ2 К1113ПВ1 |

Послідовних наближень Однократний відлік Однократний відлік Послідовних наближень |

7,5 30 100 30 |

18 64 64 18 |

0,5;0,5 0,5;0,5 -1;1 0,1;0,1 |

0,75;0,75 1;1 -1;1 -0,1;0,1 |

-3;3 -0,1;0,1 -3;3 -0,4;0,4 |

8 8 8 10 |

[4, ст.142]

З вище наведених параметрів АЦП, ми бачимо, що АЦП К1113ПВ1 має найменшу величину похибок. Крім того, це є єдина з приведених мікросхем функціонально завершена ВІС, яка містить у своєму складі компаратор напруг, ЦАП, РПН, джерело опорної напруги, ГТІ, вихідний буферний регістр з трьома станами а також логічні схеми керування, чого нема у інших мікросхем, тобто її використання дозволяє максимально спростити схему. Це є послідовний з накопиченням АЦП послідовних наближень. Мікросхема призначена для перетворення однополярного або двополярного вхідного сигналу з представленням результатів перетворення у паралельному двійковому коді. Для її експлуатації необхідні тільки два джерела живлення і регулювальні резистори. Виготовляється по біполярній технології, що модифікована для суміщеного формування на кристалі біполярних транзисторів, а також елементів інжекційної логіки і тонкоплівкових прецезійних резисторів. Технологія дозволяє розмістити в одній ВІС велике число цифрових елементів і виконувати аналогові вузли з високим рівнем параметрів. Мікросхема К1113ПВ1 випускається у 18-виводному герметичному металокерамічному корпусі типу 238.18-1 з вертикальним розташуванням виводів.

Нумерація і призначення виводів:

1-9 – цифрові виходи 2-10;

10 – напруга джерела живлення UCC1;

11 – гашення і перетворення;

12 – напруга джерела живлення UCC2;

13 – аналоговий вхід;

14 – аналогова земля;

15 – керування зсувом нуля;

16 – цифрова земля;

17 – готовність даних;

18 – цифровий вихід 1.

Номінальні напруги джерел живлення: UCC1=5В і UCC2=-15В.

Як і будь-який АЦП послідовних наближень, дана мікросхема має наступний принцип роботи: після подачі сигналу “Пуск” на виході найстаршого розряду РПН з’являється логічна одиниця. На виході ЦАП з’являється відповідна напруга. Якщо ця напруга менша Uвх , то включається логічна одиниця на виході наступного розряду регістра, інакше ця напруга знімається. Таким методом спроб перебираються всі розряди до наймолодшого.

У ВІС К1113ПВ1 вихідний струм ЦАП порівнюється з струмом, який протікає через вхідний резистор від джерела сигналу. Тим самим формується логічний сигнал керування РПН. Стабілізація розрядних струмів ЦАП здійснюється вбудованим ДОН на основі стабілітрона із закритою структурою.

Включення АЦП в режимі роботи з уніполярною вхідною напругою передбачає під’єднання виводу 15 до цифрової землі (вивід 16). При цьому на виході вбудованого ЦАП задається струм, який дорівнює струму цифрового виводу 1, але має протилежну полярність [4,ст.150].

При роботі з уніполярною вхідною напругою її величина рівна 0…+10 В.

Встановлення РПН у вихідний стан і запуск його в режим перетворення проводиться по зовнішньому сигналу “Гашення/перетворення”. По закінченню перетворення АЦП видає сигнал “Готовність даних”, і інформація з РПН поступає на цифрові виходи через каскади з трьома станами.

Часові діаграми вхідних і вихідних сигналів зображені на рис. 4.1 [4]:

рис. 4.1 Часові діаграми вхідних і вихідних сигналів АЦП

Для спряження АЦП і ЦАП з МП використаємо програмований паралельний інтерфейс (ППІ) КР580ВВ55. При програмному опитуванні АЦП можна використовувати режим 0 ППІ, а при вводі через переривання при використанні команди RST N – режим 0 або 1.

Режим роботи і напрям обміну з зовнішніми пристроями програмується керуючими словами. Керуюче слово режиму встановлює режими роботи груп А або B і режим вводу або виводу для кожного порта. Керуюче слово порозрядного встановлення або скидання порту С використовується для порозрядного вводу інформації і для початкового встановлення станів окремих розрядів порту С при його використанні для керування обміном в режимах 1, 2.[8].

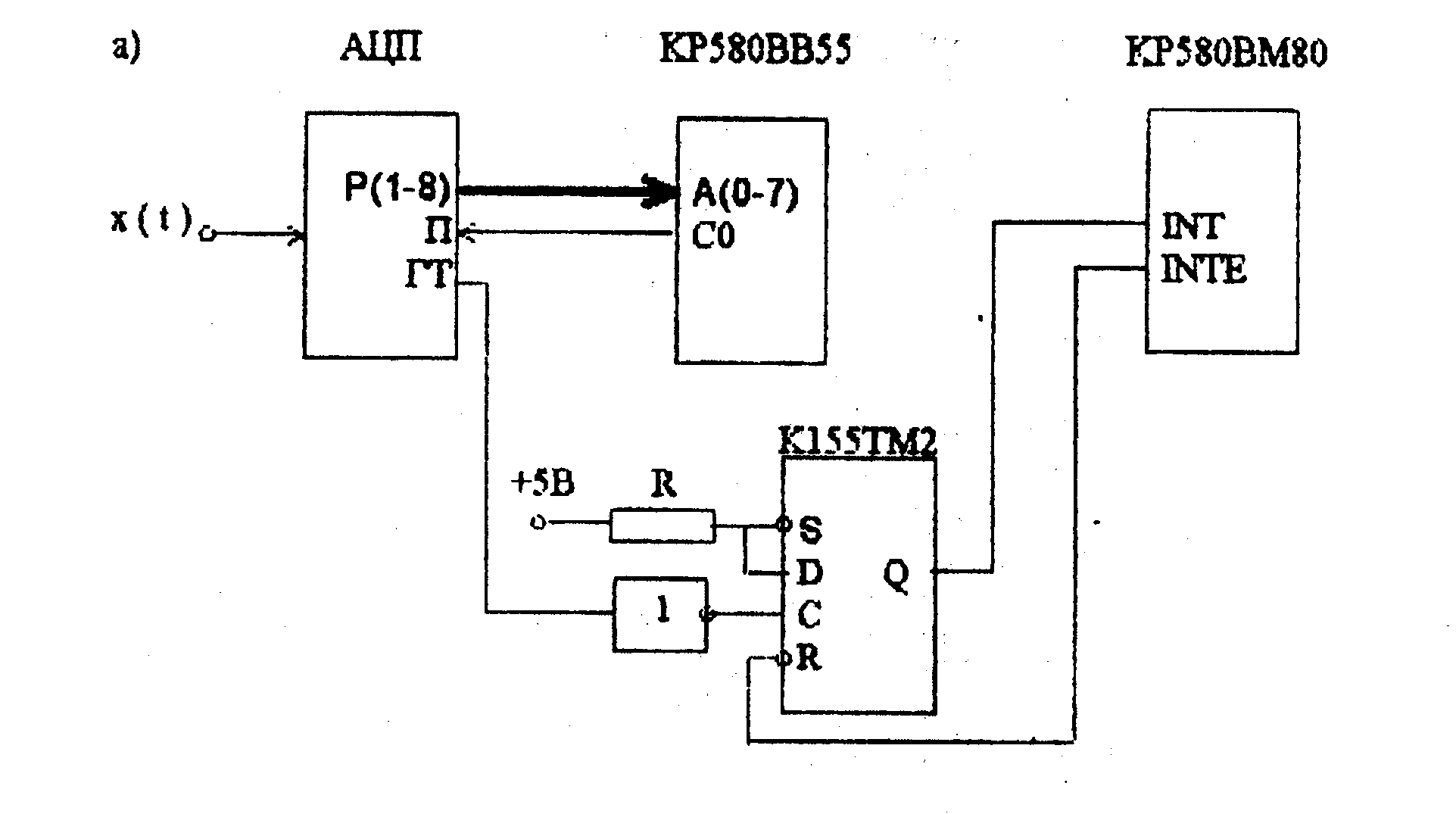

Рис 4.2 Два способи реалізації команди RST 7

Запуск АЦП (сигнал П) здійснюється через паралельний інтерфейс КР580ВВ55 (розряд 4 каналу С). ППІ використовується в режимі 0, сигнал ГТ після інвертування поступає на вхід синхронізації тригера К155ТМ2. Коли на вході “С” відбувається перехід від рівня логічного нуля до рівня логічної одиниці, дані з входу D (тобто логічна “1”) передаються на вхід Q, який з’єднаний з виводом запиту переривання INT мікропроцесора КР580ВМ80. Очевидно, що ця зміна стану тригера відбувається лише тоді, коли на вході R (виводі INTE) сигнал має рівень логічної “1”, тобто переривання дозволено.

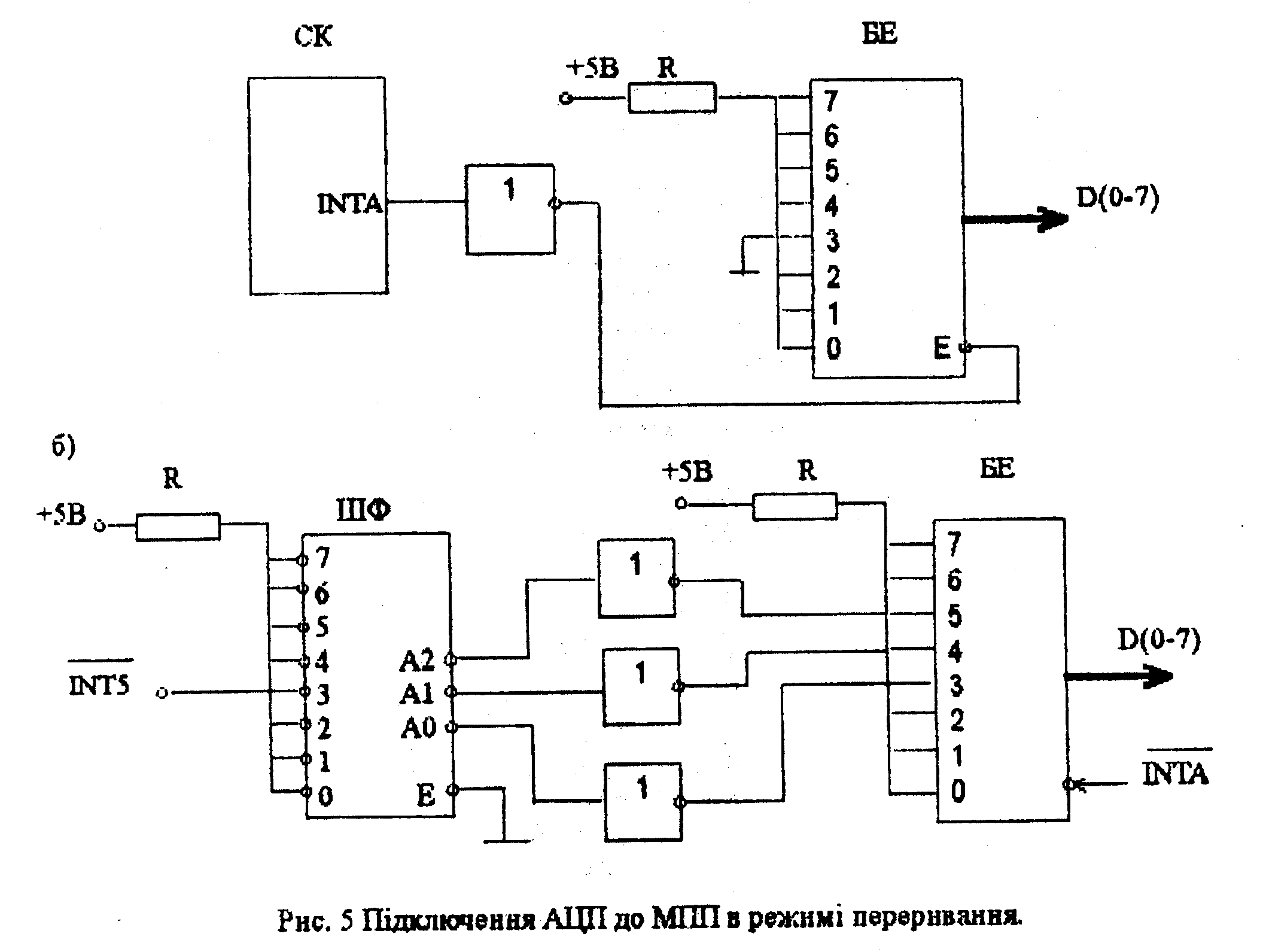

При виконанні

машинного циклу

“Підтвердження

переривання”

в керуючому

слові, яке на

початку машинного

циклу записується

в системний

контролер (СК),

розряд INTA є рівним

одиниці, що

обумовлює

формування

одноіменного

сигналу керування.

Цей сигнал

через інвертор

(якщо він є H –

активним і без

інвертора при

L – активному

сигналі) поступає

на вхід дозволу

![]() буферного

елемента (БЕ)

з трьома вихідними

станами (логічні

“0” та “1” і високого

вихідного

опору). При

буферного

елемента (БЕ)

з трьома вихідними

станами (логічні

“0” та “1” і високого

вихідного

опору). При

![]() виходи БЕ повторюють

логічні рівні

на входах 0 –

7. Як БЕ можуть

бути використані

дві мікросхеми

К155ЛП11, кожна з

яких має по

шість входів/виходів

без інвертора.

виходи БЕ повторюють

логічні рівні

на входах 0 –

7. Як БЕ можуть

бути використані

дві мікросхеми

К155ЛП11, кожна з

яких має по

шість входів/виходів

без інвертора.

Формування логічних рівнів на входах БЕ визначається номером N з команди RST N. Для реалізації коду команди RST 7 на вході 6 повинен бути встановлений рівень логічного “0”, а на всіх інших входах – рівень логічної “1”. Цей код команди МП читає не з пам’яті, а безпосередньо з МП, в результаті якої МП переходить до підпрограми обробки переривань, яка повинна бути розміщена в пам’яті адресою 8*7. Крім того, при виконанні команди RST N на виході INTE встановлюється рівень логічного “0”, який “скидає” за допомогою тригера К155ТМ2 сигнал INT. Встановити сигнал INTE=1 можна лише програмно за допомогою команди EI (дозвіл переривання), якою повинна завершуватись підпрограма обробки переривань.

При такому використанні БЕ реалізується лише один запит на переривання. Для реалізації восьмирозрядної векторної системи потрібно використовувати шифратор (ШФ) з вісьмома входами і трьома виводами (КМ155ИВ1). Для простоти використаємо перший варіант реалізації.

Підключення АЦП до шин МПП в режимі вводу інформації через переривання при використанні команди RST 7 показане на рис. 4.3.

Рис. 4.3 Підключення АЦП до шин МПП в режимі вводу інформації через переривання при використанні команди RST 7.

4.2 Вибір ЦАП

В ЦАП цифрова інформація вводиться у вигдяді паралельного цифрового коду перетворюваного числа, а аналоговий сигнал на виході є носієм інформації.

Будь-який ЦАП складається з суматора і резистивної схеми. Резистивна схема може бути реалізована двояко:

на основі зважених резисторів;

на основі матриці R-2R.

Приведемо порівняльну характеристику деяких восьмирозрядних ЦАП (так як розрядність вихідного сигналу y(t) – 8 біт):

Таблиця 4.2

|

Мікросхема |

Абс. похибка перетворен-ня, % |

Нелінійність, % |

Час встановлення вихідного струму, нс |

К-ть виво-дів |

Час затримки розповсюдження |

|

К1118ПА1 К1118ПА3 |

-5;5 -2;2 |

-0,5;0,5 -0.195;0,195 |

20 10 |

16 24 |

6 — |

[4, ст. 110]

Цих дві ВІС сумісні з логікою ЕСЛ. Для того, щоб не ускладнювати схему для узгодження з ТТЛ-логікою, я використаю 10-розрядну ЦАП, а лишні виводи заземлю.

Опишемо швидкодіючий ЦАП К572ПА1, який призначений для перетворення двійкового коду у струм, містить 10 розрядних струмових перемикачів і генератор струмів і побудований на основі матриці R-2R. Ця мікросхема характеризується малою споживаною потужністю і достатньою вихідною швидкодією (час перетворення становить 5 мкс). К572ПА1 – ЦАП перемножуючого типу. Поставляється в герметичному корпусі типу 201.16-8. Корпус металокерамічний; містить 16 виводів (двохрядне розміщення виводів). Виконанна на КМОН – технології з полікремнієвим затвором. В склад ЦАП-а входитьпрецезійна полікремнієва резистивна матриця типу R-2R, підсилювачі-інвертори (ПІ) для керування ключами, струмові двохполярні ключі, виконані на КМОН транзисторах.

Для роботи ЦАП в режимі з виходом по напрузі до ІС підключається ДОН і операційний підсилювач з колом зворотнього зв’язку, яке працює в режимі з сумуванням струмів.

Метод перетворення, що використовується в ІС К572ПА1, передбачає сумування у відповідності до заданого значення двійкового коду всіх розрядних струмів, які є зваженими по двійковому законі і пропорційних значенню опорної напруги на виводі 15.

Нумерація і призначення виводів мікросхеми:

1-2 – аналогові виходи;

3 – земля;

4-13 – цифрові входи;

14 – напруга живлення;

15 – опорна напруга UREF;

16 – вивід резистора зворотнього зв’язку;

Ucc=-5,2В, UREF=-15В, струм споживання – 2мА.

Значення струмів на виводах 1 і 2 в результаті цифро-аналогового перетворення визначаються за формулами:

![]() (4.1)

(4.1)

![]() , (4.2)

, (4.2)

де ![]() – значення

двійкового

розряду на

цифровому

виводі

– значення

двійкового

розряду на

цифровому

виводі

![]() ,

,

![]() - інверсне

значення,

- інверсне

значення,

UR – значення опрної напруги.

Двійковий закон розподілення струмів зберігається при умові рівності виходів 1 і 2. Це забезпечує підключенню виводу 1 до інвертованого входу ОП, який включений у ланцюг зворотнього зв’язку. Неінвертований вхід ОП з’єднується з виходом 2 із шиною аналогової землі. При цьому здійснюється перетворення струму на виході 1 на пропорційну йому напругу на виході ОП. Резистор зворотнього зв’язку визначає значення коефіцієнта значення перетворення і напругу у кінцевій точці шкали.[4, ст.50]

При появі на одному з виходів ЦАП напруги високого рівня струм відповідної гілки резистивної матриці поступає на вихід 1, а при подачі низького рівня – на вихід 2. Для досягнення стабільності основних параметрів перетворення при впливі зовнішніх дестабілізуючих факторів до мікросхеми підключають резистор зворотнього зв’язку. В ЦАП КР580ПА1 він може бути розміщений всередині мікросхеми або підключатися ззовні,

При вживанні

джерела опорної

напруги

![]() з використання

підключення

резистора

зворотнього

зв’язку,

розміщеного

на кристалі,

крок квантування

мікросхеми

складає 10мВ. В

режимі однополярного

сигналу вихідна

напруга визначається

за формулою:

з використання

підключення

резистора

зворотнього

зв’язку,

розміщеного

на кристалі,

крок квантування

мікросхеми

складає 10мВ. В

режимі однополярного

сигналу вихідна

напруга визначається

за формулою:

![]() ,

тобто зв’язок

між вихідною

напругою і

двійковим кодом

є таким:

,

тобто зв’язок

між вихідною

напругою і

двійковим кодом

є таким:

000…00 0

000…01 2-8UREF

100…00 2-1UREF

111…11 (1-2-8) UREF.

UREF по окремих гілках задає значення струму.

Варіант схеми підімкнення ЦАП до МП пристрою, який забезпечує уніполярний вихід, зображений на малюнку:

Рис. 4.4 Схема підімкнення ЦАП до МПП

В даній

схемі конденсатори

С1, С2, С3 використовуються

для знищення

завад у ланцюгах.

В якості С2 і

С3 можуть виступати

К520-24, а в якості

С1 – КМ-56-П33. Для

захисту виводів

1 і 2 ЦАП від випадкового

попадання

від’ємної

напруги їх

підключають

через обмежувачі

на діодах Шоткі

(наприклад, це

може бути мікросхема

КД514А).

Для нормальної роботи ЦАП використовують зовнішні елементи: ІОН, струмозадаючий резистор, конденсатор частотної корекції, резистор компенсації зміщення нуля.

5. Програма

вводу інформації

через АЦП

і виводу через

ЦАП

Для спряження

АЦП і ЦАП з МП

доцільно використати

програмований

паралельний

інтерфейс (ППІ)

КР580ВВ55. При програмному

опитуванні

АЦП можна використати

режим 0 ППІ, а

при вводі через

переривання

- режим 0 або 1. В

залежності

від значень

розрядів керуючого

слова 4, 3, 1, 0 можливі

16 різних комбінацій

схем вводу/виводу.

При вводі інформація

від зовнішніх

пристроїв не

запам’ятовується

в регістраї

портів, а передається

безпосередньо

на шину даних

по сигналу

читання на

вході

![]() .

Інформація

на входах портів

повинна бути

встановлена

до появи сигналу

читання і зберігатись

після його

закінчення.

ППІ в режимі

0 використовується

для побудови

програмних

каналів вводу/виводу

з обслуговуванням

по програмі.

[8]

.

Інформація

на входах портів

повинна бути

встановлена

до появи сигналу

читання і зберігатись

після його

закінчення.

ППІ в режимі

0 використовується

для побудови

програмних

каналів вводу/виводу

з обслуговуванням

по програмі.

[8]

Так як ввід/вивід здійснюється за допомогою паралельного інтерфейсу, то для проведення даної операції треба ініціалізувати КР580ВВ55. Керуюче слово виглядає так:

Рис. 5.1 Керуюче слово ініціалізації ППІ

Виберемо наступні адреси портів:

А – А0Н;

В – A1H;

С – A2H;

РКС – A3H.

Керуюче слово заноситься в РКС такою послідовністю команд:

MVI A, 90H

OUT 0A3H

Операція вводу:

IN 0A0H; ввід з каналу А

STA 500Н; вивід по адресі XN значення xn

Операція виводу:

LDA 504Н ;ввід в акумулятор 8-розрядів Yn з комірки YN

OUT 0А1H ;вивід в канал В;

Розряд 4 каналу С керує роботою АЦП (до нього підключений вивід АЦП “гашення/перетворення”).

Тоді гашення програмується так:

MVI A ,9H ;вивід в С4 одиниці

OUT 0A2H

Перетворення програмується так:

MVI А, 8H ;вивід в C4 нуля

OUT 0A2H

Як вже було зазначено, коефіцієнти а0, b0, C0 та змінні xn, yn-1, yn-2, yn представляються у пам’яті у вигляді таблиці з початковою адресою 500H.

Програмно це реалізовано так:

|

ORG 100H MVI A, 90H OUT 0A0H MVI A, a0 STA 501H MVI A, b0 STA 502H MVI A, c0 STA 503H LXI SP, 4FFH |

;занесення коефіцієнту а0 ;занесення коефіцієнту b0 ;занесення коефіцієнту c0 |

6. Програма цифрової обробки інформації.

Аналізуючи алгоритм функціонування МП–пристрою, ми бачимо, що нам потрібно використовувати такі операції:

множення однобайтового слова на однобайтове;

додовання однобайтових слів (це можна здійснити за допомогою команди ADD).

В [2] наведені готові програми для здійснення цих операцій.

1. Множення однобайтових чисел без знаку:

|

B |

|

|

* |

|

|

A |

|

|

H |

L |

|

10 7 7 10 4 16 10 5 16 10 |

MULL88: Z1: Z2: |

LXI H, 0 MVI D, 0 MVI C, 8 DAD H RLC JNC Z2 DAD D DCR C JNZ Z1 RET |

Коефіцієнти а0, b0, c0в пам'яті зберігаються у вигляді модуля.

Основна програма враховує, що c0 є від'ємний.

Користуючись алгоритмом програми обробки переривання і вищесказаним, програма обробки переривання на мові асемблеру буде (вона зберігається за адресою 8*7)[8]:

|

4 11 11 10 5 16 7 10 10 10 4 10 |

OP: |

D1 PUSH H PUSH PSW IN 0A0H LDA 500H SHLD XNI MVI A, 9H OUT 0A2H POP PSW POP H EI RET |

;заборона переривань ;Ввід

в програму

розрядів X0 ;гашення результату ;Дозвіл переривання |

Основна програма, за алгоритмом, починається з ініціалізації мікросхеми K580ВВ55 для обміну з ЦАП і АЦП, після того АЦП встановлюється (після гасіння) в режим перетворення вхідного сигналу. Далі іде циклічний підрахунок і виведення результату.

Основна програма:

|

7 7 13 7 13 7 13 10 7 10 7 10 7 10 13 5 13 17 13 13 5 13 17 13 4 13 13 5 13 17 13 4 13 13 13 13 13 13 10 5 10 10 7 |

START: |

ORG 100,H MVI A, a0 STA 501H MVI A, b0 STA 502H MVI A, c0 STA 503H LXI SP, 4FFH MVI A, 90H OUT 0A3H MVI A, 9H OUT 0A2H MVI A, 8H OUT 0A2H LDA 500H MOV B, A LDA 501H CALL MULL88 STA 504H LDA 505H MOV B, A LDA 502H CALL MULL88 LDA 504H ADD H STA 504H LDA 503H MOV B, A LDA 506H CALL MULL88 LDA 504H SUB H STA 504 H LDA 505H STA 506H LDA 504H STA 505H LDA 504H OUT 0A1H MOV A, 8H OUT 0A3H JMP START HLT |

; занесення в пам’ять коефіцієнтів ; ініціалізація ППІ ; запуск АЦП ;занесення в програму xn ; занесення коефіцієнту а0 ; визначення a0*xn ; занесення в комірку для yn ; занесення в програму значення yn-1 ; занесення коефіцієнту b0 ; визначення b0*yn-1 ; додавання b0*yn-1 і а0*хn ; занесення в комірку для yn ; занесення коефіцієнту с0 ; занесення в програму значення yn-2 ; визначення с0*yn-2 ; визначення b0*yn-1 + а0*хn - с0*yn-2 ; занесення в комірку для yn ; занесення yn-1 в комірку для yn-2 ; занесення yn в комірку для yn-1 ; вивід результату

; вивід

логічного 0

в розряд С4 для

; перехід на початок |

6.1 Оцінка верхньої граничної частоти фільтру

Оцінку проводимо з точки зору найнижчої швидкодії фільтру. В процесі виконання програми виконується:

підпрограма обробки переривань (ОР)

підпрограма множення (3 рази) (MULL88)

Кількість тактів, за які виконується програма, зведені в таблицю:

Таблиця 6.1

|

Назва

|

Кількість тактів, необхідних для виконнаня програми |

Число виконань даної програми за один цикл |

Кількість тактів, за цикл виконання програми |

|

Основна програма |

400 |

1 |

400 |

|

MULL88 |

95 |

3 |

285 |

|

OP |

108 |

1 |

108 |

Кількість тактів для виконання кожної команди взято з [6].

Формулювання теореми Котельникова:

будь-який сигнал, який має скінчений спектр, може бути без втрат перетворений у цифрову форму і потім відтворений за відліками цього дискретного сигналу при умові:

![]() (6.1)

(6.1)

Для виконання програми необхідно всього тактів N=793. Для максимальної частоти f=2.5МГц для МП KР580ВМ80, частота видачі інформації fвид=2,5МГц/793=3152,6 Гц

За теоремою Котельникова, верхня гранична частота для фільтра складає

fверхнє = fвид /2=3152,6/2=1576,3 Гц (6.2)

7.

Опис фрагменту

принципової

схеми

реалізації

системного

контролера.

Системний контролер КР580ВВ28 виконує три функції:

фіксація слова стану процесора;

буферизація шини даних;

формування частини сигналів, які належать шині керування МПС (при звернені до ЗП –

і

і

,

при звернені

до пристроїв

вводу/виводу

-

,

при звернені

до пристроїв

вводу/виводу

-

і

і

,

,

).

).

Системний контролер складається з двонаправленої буферної схеми даних, регістра стану, і декодуючої схеми.

Восьмирозрядна

паралельна

тристабільна

буферна схема

даних приймає

інформацію

з канала даних

МП по виводам

D7 – D0 і передає

в регістр стану

інформацію

стану, на системний

канал даних

по виводам DB7

– DB0 видає дані

у циклі запису

по сигналу

![]() .

В циклі читання

по сигналу

.

В циклі читання

по сигналу

![]() заперечення

буферна схема

приймає дані

з системного

каналу по виводам

DB7 – DB0 і передає

по виводам D7 –

D0 на канал даних

мікропроцесору.

заперечення

буферна схема

приймає дані

з системного

каналу по виводам

DB7 – DB0 і передає

по виводам D7 –

D0 на канал даних

мікропроцесору.

Регістр

стану по вхідному

сигналу

![]() фіксує інформацію

стану МП в такті

Т1 кожного машинного

циклу МП.

фіксує інформацію

стану МП в такті

Т1 кожного машинного

циклу МП.

Декодуюча

схема формує

один з вище

перелічених

сигналів керування.

Асинхронний

сигнал

![]() керує видачею

даних з буферної

схеми і керуючих

сигналів з

дешифратора:

при наявності

низького рівня

на вході

керує видачею

даних з буферної

схеми і керуючих

сигналів з

дешифратора:

при наявності

низького рівня

на вході

![]() буферна схема

передає дані

і формує один

з керуючих

сигналів; при

напрузі високого

рівня всі виходи

мікросхеми

переходять

у високоімпендансний

стан. Напруга

високого рівня

на вході

буферна схема

передає дані

і формує один

з керуючих

сигналів; при

напрузі високого

рівня всі виходи

мікросхеми

переходять

у високоімпендансний

стан. Напруга

високого рівня

на вході

![]() переводить

виходи

переводить

виходи

![]() ,

,

![]() ,

,

![]() у пасивний стан

(напругу високого

рівня) і блокує

передачу інформації

через буферну

схему даних.

у пасивний стан

(напругу високого

рівня) і блокує

передачу інформації

через буферну

схему даних.

Керуючі

синали

![]() і

і

![]() формуються

в циклі запису

по сигналу

формуються

в циклі запису

по сигналу

![]() .

.

При роботі

з МП КР580ВМ80А

системний

контролер у

циклі підтвердження

запиту переривання

формує три

сигнали

![]() для прийому

трьох байтів

команди CALL від

контролера

переривань

КР580ВН59 [7].

для прийому

трьох байтів

команди CALL від

контролера

переривань

КР580ВН59 [7].

В невеликих

мікропроцесорних

системах вихід

![]() мікросхеми

КР580ВК28 можна

під’єднати

до напруги +12В

через резистор

опору

мікросхеми

КР580ВК28 можна

під’єднати

до напруги +12В

через резистор

опору

1 кОм. Під

час дії сигнала

RC буферна

схема даних

мікросхеми

формує код

команди RST

7 і передає на

канал даних

МП. Таким чином,

мікромхема

забезпечує

єдиний вектор

переривань

з номером 7 без

додаткових

компонентів.

Основні параметри мікросхеми зведені у таблицю:

Таблиця 7.1 Параметри КР580ВК28

|

Параметр |

Значення |

|

Вихідний струм високого рівня Вихідна напруга високого рівня на виходах D0-D7 Струм споживання Вхідна ємність

Довжина

сигналу

Час

встановлення

сигналів

Час затримки інформації на виходах DB0-DB7 Час збереження інформації на виходах DB0-DB7 Час встановлення інформації на виходах DB0-DB7 Час встановлення вхідної інформації на виходах D0-D7 відносно RC в режимі читання |

-10мкА 3,6В 140мА 12пФ 22нс 40нс 30нс 20нс 30нс 45нс |

Структурна схема системного контролера зображена на рис. 7.1.

Рис.7.1 Структурна схема системного контролера КР580ВВ28

Рис. 7.2 Схема підкдючення КР580ВВ28 до МП КР580ВМ80А

Опис виводів мікросхеми:

Таблиця 7.2

|

Вивід |

Позначення |

Тип виводу |

Функціональне призначення |

|

1 2 3 4 5, 7, 9, 11, 13, 16, 18, 20 6, 8, 10, 12, 15, 17, 19, 21 14 22 23 24 25 26 27 28 |

RC DB4, DB7, DB3, DB2, DB0, DB1, DB5, DB6 D4, D7, D3, D2, D0, D1, D5, D6 GND

Ucc |

вхід вхід вхід вхід вихід/ вхід вхід/ вихід — вхід вихід вихід вихід вихід вихід вхід |

Стробуючий сигнал стану Підтвердження захвату Видача інформації Прийом інформації Канал даних системи Канал даних мікропроцесора Загальний Управління передачею даних і видачею сигналів Підтвердження запиту переривання Читання з ЗП Читання з ПВВ Запис в ЗП Запис в ПВВ Напруга живлення +5В |

висновок

Отже, цифрові фільтри мають ряд переваг над аналоговими:

1) нечуттєвість характеристик фільтра до розкидування параметрів елементів, що у нього входять, їх часових та температурних дрейфів;

2) малі розміри і висока надійність фільтрів, пов’язані з використанням ВІС;

3) легкість зміни параметрів і характеристик цифрового фільтру через модифікацію програми і коефіцієнтів;

4) можливість реалізації фільтрів із змінними в процесі роботи параметрами.

Рівняння даного цифрового фільтру є дуже просте як для розв’язку, так і для реалізації. Проте, як видно з приведеної оцінки верхньої граничної частоти фільтру, вона не є достатньо високою. На неї впливає, по-перше, низька тактова частота МП КР580ВМ80, а, по-друге, велика кількість рядків програми. Це частково пояснюється відсутністю операції множення в МП КР580ВМ80.

Крім

того, недоліком

ЦФ є те, що кінцевий

час перетворення

сигналу за

допомогою АЦП

і ЦАП і особливо

час, який необхідний

для програми

обчислення

![]() ,

обмежують знизу

період

,

обмежують знизу

період

![]() між сусідніми

замірами вхідного

сигналу і значеннями

вихідного. Це

в свою чергу

обмежує верхню

граничну частоту

сигналу

між сусідніми

замірами вхідного

сигналу і значеннями

вихідного. Це

в свою чергу

обмежує верхню

граничну частоту

сигналу

![]() ,

фільтрація

якого може бути

проведена.

,

фільтрація

якого може бути

проведена.

Так як задана розрядність (8) дорівнює розрядності МП КР580ВМ80, то це не створює ніяких ускладнень для розв’язку поставленого завдання.

Список літератури

Алексенко А. Г., Галицин А. А., Иванников А. Д. Проектирование радиоелектронной апаратуры на микропроцессорах: програмирование, типовые решения, методы отладки. М.; Радио и связь, 1984.

Майоров В. Г., Гаврилов А. И. Практический курс программирования микропроцессорных систем. М.; Машиностроение, 1989.

Корячко В. П. Микропроцессоры и микроЭВМ в радиоэлектронных средствах; Учеб. Для вузов по спец. ‘Конструирование и технология радиоэлектронных средств.’ М.; Внеш. Шк, 1990.

Федорков Б. Г., Телец В. А. Микросхемы ЦАП и АЦП: функционирование, параметры, применение. М; Енергоатомиздат, 1990.

Коффон Д. Технические средства микропроцессорных систем; Практический курс. Пер. с англ. М.; Мир, 1983.

Програмное обеспечение микропроцессорных систем. Справочник С.Д. Погорелый, Т.Ф.Слободянюк, Києв, “Техника”, 1989.

Полупроводниковые БИС запоминающих устройств; Справочник В. В. Баранов, Н. И. Бекин, А. Ю. Гордунов и др.: Под ред. А. Ю. Гордонова и Ю. Н. Дьякова. М.; Радио и связь, 1987.

Проектирование микропроцессорной электронно-вычислительной аппаратуры: справочник В. Г. Артюхов, А. А. Будняк, В. Ю. Лапий и др. К.; Техника, 1988.

Г. Деч Руководство по практическому применению преобразований Лапласа, М. 1964.

додатки

MVI A ,91H - вивід в С4 одиниці

OUT FBH - вивід в С4 одиниці

MVI А, 8H вивід в C4 нуля

OUT FBH вивід в C4 нуля

Після цього АЦП приступив до перетворення вхідного сигналу в цифровий код. По закінченні

перетворення МП переходить до програми обробки перетворешія. в якій послідовно вводиться 2 байти Хn;

IN F8H ;ввід з каналу А

STA XNL ;вивід по адресі XNL - молодшого байту Хn

IN FAH ;ввід з каналу С

ANI 03Н

STA XNH ; вивід по адресі XNH - адреси старшою байту Хn

операція виводу виглядає простіше:

LDA YN1 ; ввід в акумулятор 8-розрядів Yn з комірки YN1

OUT F9H ; вивід в канал В;

LDA YN2 ; ввід в акумулятор 2-х молодших розірядів YN3,YN2

;(iншi занулені крім С4) OUT FBH

Передача (двох) 2-х молодших розрядів Yn, окремо зумовлена тим, щоб була найменша похибка у вихідному сигналі оскильки AЦП виводить інформацію швидко. Передача 2-х. старших розрядів Yn окремо викликала б (значну похи6ку) стрибок вихідною сигналу.

6.Програма цифрової обробки інформації.

Як видно зі схеми алгоритми функціонування NМП-пристрою, програма цифрової оброб-ки iнформації повинна неодноразово виконувати такі операції як :

1) множення 2-байтвох чисел на однобайтові;

2) додавання 2-х байтових чисел.

Для цього можна використати готові програми [2] ПП множення цилих чисел без •знаку 16*8:

|

D |

E |

|

|

* |

||

|

A |

||

|

A |

H |

I |

|

DMULT: NXBIT: NOADD: |

LXI Н, 0H MVI С, 08Н DAD H RAL JNC NOADD DAD D AСІ 0 DCR С JNZ NXBIT RET |

ПП додавання двобайтових чисел:

|

B |

С |

|

|

+ |

||

|

адрHL+1 |

адрHL |

|

|

адрHL+1 |

адрHL |

|

| PLUS: |

MOV A, C ADD M MOV M, A MOV А, В INX H ADC M MOV M, A DCX H RET |

Виходячи, що з умови завдання вхідний сигнал - двополярний. то потрібно організувати операцію множення 2-го числа на однобайтове зі знаком. Оскільки вхідний сигнал представле-ний як 10-ти розрядний зі знаком, а є можливість використати ПП множення DMULT чисел 16*8 біт знаку, то при множенні будемо подавати як ціле додатнє число, за модулем рівне. В па-м'яті будемо зберігати в такому форматі:

|

байт XNH |

байт XNL |

|||||||||||||||||||

|

D15 |

D8 |

D7 |

D0 |

|||||||||||||||||

|

0 |

0 |

1 |

0 |

0 |

0 |

. |

. |

. |

. |

. |

. |

. |

. |

. |

||||||

модуль Xn

|

(адр.XNH=адр.XNH1) |

З АЦП Xn подається у такому вигляді:

111…11 +Umax

100…00 0

000…00 -Umax

Для приведення цього формату потрібно:

1)

коли X9=0

то проінвестувати

розряди X0![]() X9;

D15=1

X9;

D15=1

2) коли X9=1 то D15=0; X9=0

Користуючись алгоритмом програми обробки переривання і вищесказаним, програма обробки переривання на мові асемблеру буде:

|

OP: M1: M2: |

PUSH H PUSH PSW LHLD XNL SHLD XNLP IN F8H MOV L, A IN FAH ANI 03H MOV H, A ANI 02H JZ M1 MOV A, H ANI 010 MOV H, A JMP M2 MOV A, L CMA MOV L, A MOV A, H CMA MOV H, A SHLD XNI MVI A, 9H OUT FBH POP PSW POP H EI RET |

Занесення колишнього значення Xn в комірку пам’яті для Xn-1

Ввід в програму

розрядів X0

Ввід з каналу

C

розрядів

Визначення

умови:

Корекція

старшого

байту Корекція від’ємного Xn до прийнятого формулою Xn Запис Xn у комірку пам’яті XNI і XNH Вивід у канал C розряд C4=1 для гашення результату Дозвіл переривання |

Основна програма повинна функціонувати по алгоритму, наведеному вище. Виникає тільки проблема узгодження інформації (кодів) представлення чисел з АЦП в пам'яті для виводу на АЦП (а вони всі різні). Для представлення Yn в пам'яті, виберемо той же формат, що і для Хn (так само і Хn-1). Коефіцієнти а0, а1, b1 в пам'яті зберігаються у вигляді модуля.

Основна програма враховує, шо а1, є від'ємний. В основній програми будуть використані ще дві програми:

1) ПП переводу 2-х байтового числа в доповнений код (для спрощення операції додавання)

| DOP: |

MOV A, H СМA MOV H, А MOV A, І СМА MOV L, A INX H RET |

2) ПП множення чисел зi знаком, яка використовує ПП DMULT (множення чисел без знака)

|

MN ML MM |

MOV C, A MOV A, H JP ML MVI B, 1H ANI 7FH MOV H, A JMP MM MVI B, 0H XCHG MM MOV A, C CALL DMULT MOV L, H MOV H, A MOV A, B RET |

Множник

з регістру А

заноситься

в

Чи виконується

умова, що множене B=1 означає що множене (в HL) є від’ємне Корекція множеного до модуля Числа B=0 означає, що множене (в HL) є додатнє Обмін DE HL Занесення в регістр А множника з регістру С Множення чисел без знаку (16*8)

Корекція

результату

(добутку)

Ознака

знаку множеного

в А=1 – від’ємне |

Основна програма починається з ініціалізації мікросхеми K580ВВ55 для обміну з ЦАП і АЦП, після тогоАЦП встановлюється (після гасіння) в режим іперетворення вхідного сигналу. Далі іде циклічний підрахунок і виведення результату.

Основна програма.

|

M00 M0 M3 M4 M5 |

MVI A, 91H OUT FBH MVI A, 9H OUT FBH Mvi A, 8H OUT FBH LHLD XNPL LDA Al CALL MN JNZ M3 CALL DOP SHLD AXNP LHLD YNPL LDA B1 CALL MN JZ M4 CALL DOP SHLD BYNP LHLD XNL LDA A0 CALL MN JZ M5 CALL DOP MOV B, H MOV C, L I.XI H, AXNP CALL PLUS LDA BYNP MOV C, A LDA BYNP + 1 MOV B, A CALL PLUS LHLD AXNP MOV A, H ANI 7FH CMA MOV H, A MOV A, L CMA MOV L, A |

ініціалзація ВВ355 запуск АЦП занесення в HL значення Xn-1 в комірку пам’яті занесення в аккумулятор байту а1 з пост. комірки множення а1 * Xn-1 перевірка чи Xn-1 був від’ємним перетворення а1 * Xn-1 в доповнюючий код запис добутку а1 * Xn-1 в пам’ять для зберігання занесення в HL значення Yn-1 в пам’ять занесення в регістр А байту число b1 з пам’яті множення b1*Yn-1 перевірка чи Yn-1 було додатнє перетворення b1*Yn-1 в доповнюючий код запис добутку b1*Yn-1 в пам’ять для зберігання запис в HL значення Xn з комірки пам’яті запис в аккумулятор байт коеф. множення а0*Xn перевірка чи Xn був додатній перетворення в доповнюючий код

значення

добутку а0*Xn

в доповнюючому занесення в HL, добутку а1*Xn-1 в доп. Коді а0*Xn + а1*Xn-1 результат в М; М+1 занесення в регістрову пару BC b1*Yn-1 додавання b1*Yn-1 результату Yn в доп. Коді Yn HL (результат був в комірці для а1*Xn-1) Перетворення Yn (який знаходиться в доп. Коді) в код для виводу на ЦАП |

|

M15 M16 M7 M8 M9 M10 M11 M12 |

LDA AXNP+l JP M15 MOV B, H MOV C, L JMP M16 LDA AXNP MOV C, A LDA AXNP+l MOV B, A MOV A, C STA YNPL MOV A, B STA YPPH MOV A, L ANI 01H Jz M7 MVI A, 07H JMP M8 MVI A, 0CH OUT FBH MOV A, L ANI 02H JZ M9 MVI A, 0FH JMP M10 MVI A, 0EH OUT FBH MOV A, L ANI FCH MOV L, A MOV A, H ANI 01H ADD L MOV L, A MOV A, H JM M 11 MVI A, 02H ADD L JMP M12 MOV A, L 0UT F9H MVI A, 08H OUT FB JMP M0 |

Перетворення Yn в код у якому значення Yn зберігається в пам’яті Занесення значення Yn в комірку пам’яті для Yn-1 Вивід в розряд C6 каналу С молодшого розряду Y0 результату Yn Вивід в розряд C7 каналу С молодшого розряду Y1 результату Yni Вивід в канал B розрядів Y2…Y9 результату наступним чином Y8 B0 Y9 B1 Y2 B2 Y3 B3 ……………… Y7 B7 Вивід логічного 0 розряд С4 каналу С для дозволу перетворення АЦП перехід на початок |

Множення однобайтових чисел

|

MULL88: NXBIT: NOADD: |

MVI B, 0 MVI E, 8 MOV A, C RAR MOV A, C DCR E RM MOV A, B JNC NOADD ADD D RAR MOV B, A JMP NXBIT |

Додавання цілих 8-розрядних зі знаком [2, 222]

|

ADSIG M2: M3 MUSIG |

MVI C, 02H MOV A, D ANA A JM M1 DCR C MOV B, A MOV A, E ANA A JM M1 ADD B JM M4 MOV A, C XRA D ANI 80H PUSH PSW MOV A, C ANI 7FH MOV C, A MOV A, D ANI 7FH MOV D, A CALL MUL88 POP PSW ORA B RET |

Перевід у доповнюючий код (в DE)

|

CMPL |

MOV A, D CMA MOV D, A MOV A, E CMA MOV E, A INX D RET |

В силу наведених порівнянь ми бачимо, що мікросхема К572ПВ3 краща з точки зору швидкодії. Тому ми будем використовувати дану мікросхему. К572ПВ3 виконана по технології КМОН, випускається у 18-вивідному корпусі з вертикальним розміщенням виводів. Крім того, дана АЦП містить у своєму складі ГТІ, компаратор напруг, буферний регістр з трьма станами (0, 1, високий імпенданс), РПП, ЦАП, логічні схеми керування і синхронізації, чого немають у своєму скдаді інші перераховані мікросхеми. Вона побудована таким чином, що АЦП забезпечує основні умови спряження з МП:

довжина цифрового слова на виході перетворювача відповідає довжині слова базових типів ВІС МП;

керування його роботою здійснюється безпосередньо сигналами від МП з мінімальними апаратними і програмними затратами;

часові характеристики АЦП добре співпадають з часовими характеристиками більшостів ВІС МП;

цифрові виходи перетворювача допускають пряме підключення до вхідних портів і шини даних МП.

Логічні схеми керування і синхронізації регламентують весь процес перетворення і узгодження АЦП з зовнішніми пристроями. ГТ обслуговує процес перетворення і обміну даними. Ддя роботи АЦП потрібно ІОН, однополярне живлення та декільна регістрів.

Ucc=4,75-5,25. Робоча тактова частота генератора 500 кГц задається зовнішніми RC елементами.

Номерація і опис виводів:

1-3 – цифрові виводи 4-2;

4 – цифровий вивід 1;

5 – вивід

стану

![]() ;

;

6 – вхід

кеоування

![]() ;

;

8 – вхід тактування CLK;

9 – цифрова земля DGND;

10 – напруга джерела живлення Ucc;

11 – опорна напруга UREF;

12 – вхід зміщення характеристик BOFS;

13 – аналоговий вхід ULEF;

14 – аналогова земля AGND;

15 – цифровий вхід 8;

16-18 – цифрові виходи 7-5.

Мікросхема АЦП здатна працювати з внутрішнім так і зовнішнім ГТІ.

Алгоритм перетворення АЦП реалізується за допомогою регістра послідовних наближень, який включає регістер зсувів і регістра пам’яті на RS-тригерах. В ньому виконується операція порозрядного зсуву логічної одиниці у напрямку від старших розрядів до молодших, збереження результату перетворення і порозрядного запису стану КН при порівнянні вхідної аналогової напруги АЦП з напругою на виході ЦАП.

Логічні

схеми керування

і синхронізації

регламентують

вест процес

перетворення

і узгодження

АЦП з зовнішніми

пристроями

з їх допомогою

при появі зовнішніх

сигналів

![]() формуються

сигнали внутрішнього

керуваня: скидання,

початок перетворення,

управління

буферним регістром

і вихідним

сигналом

формуються

сигнали внутрішнього

керуваня: скидання,

початок перетворення,

управління

буферним регістром

і вихідним

сигналом![]() .

.

По сигналу скидання АЦП встановлюється у вихідний стан, при якому в РПП записаний код 10…00. По сигналу початку перетворення запускається внутрішній асинхронний ГТІ, який обслуговує проце перетворення і обміну даними.

При часовому співпадінні вище перерахованих сигналів формується сигнал керування регістром з логікою на три стани.

Внутрішнє ГТІ побудоване таким чином, що по сигналу запуска перший від’ємний перепад тактового імпульса встановлює старший розряд у відповідний стан, після чого без додаткових часових витрат починається обробка інформації у другому розряді і т.д..

Часові характеристики ІС:

час встановлення АЦП у початковий стан – 2 мкс;

час затримки зчитування даних – 120 нс;

час затримки скидування даних – 80 нс.

|

7 10 7 10 7 10 16 13 17 17 16 16 13 17 17 16 16 13 17 17 5 5 10 17 13 5 13 5 17 16 5 7 4 5 5 4 5 |

M00: M0: M3: M4: M5: |

MVI A, 90H OUT 0A3H MVI A, 9H OUT 0A3H Mvi A, 8H OUT 0A3H LHLD YNP2 LDA C0 CALL MULL88 CALL CMP SHLD CYNP LHLD YNPL LDA B0 CALL MULL88 CALL CMP SHLD BYNP LHLD XNL LDA A0 CALL MULL88 CALL CMP MOV B, H MOV C, L LXI H, CYNP CALL ADSIG LDA BYNP MOV C, A LDA BYNP + 1 MOV B, A CALL ADSIG LHLD CYNP MOV A, H ANI 7FH CMA MOV H, A MOV A, L CMA MOV L, A |

;ініціалзація ВВ355 ;запуск АЦП ;занесення в HL значення Yn-2 в комірку пам’яті ;занесення в аккумулятор байту а1 з пост. Комірки ;множення c0 * Yn-2 ;перетворення c0 * Yn-2 в доповнюючий код ;запис добутку c0 * Yn-2 в пам’ять для зберігання ;занесення в HL значення Yn-1 в пам’ять ;занесення в регістр А байту число b0 з пам’яті ;множення b0*Yn-1 ;перетворення b0*Yn-1 в доповнюючий код ;запис добутку b0*Yn-1 в пам’ять для зберігання ;запис в HL значення Xn з комірки пам’яті ;запис в аккумулятор байт коеф. ;множення а0*Xn ;перетворення в доповнюючий код ;значення

добутку а0*Xn

в доповнюючому ;занесення в HL, добутку c0*Yn-2 в доп. коді ;а0*Xn + c0*Yn-2 результат в М ;занесення в регістрову пару BC b0*Yn-1 ;додавання b0*Yn-1 результату Yn в доп. коді ;Yn HL (результат був в комірці для c0*Yn-2) ;Перетворення Yn (який знаходиться в доп. коді) ;в код для виводу на ЦАП |

|||

|

13 10 5 5 10 13 5 13 5 5 13 5 13 5 7 10 7 10 7 10 7 10 5 7 5 5 7 4 5 5 10 7 4 10 5 10 7 10 10 |

M15: M16: M7: M10: M11: M12: |

LDA AXNP+l JP M15 MOV B, H MOV C, L JMP M16 LDA CYNP MOV C, A LDA CYNP+l MOV B, A MOV A, C STA YNPL MOV A, B STA YPPH MOV A, L ANI 01H JZ M7 MVI A, 07H JMP M8 MVI A, 0CH JMP M10 MVI A, 0EH OUT 0A3H MOV A, L ANI FCH MOV L, A MOV A, H ANI 01H ADD L MOV L, A MOV A, H JM M 11 MVI A, 02H ADD L JMP M12 MOV A, L 0UT 0A2H MVI A, 08H OUT 0A3H JMP M0 |

;Перетворення Yn в код у якому значення Yn ;зберігається в пам’яті ;Занесення значення Yn в комірку пам’яті для Yn-1 ;Вивід в розряд C6 каналу С молодшого розряду Y0 ;результату Yn ;Вивід в канал B розрядів Y2…Y9 результату ;наступним чином ;Y0 B0 ;Y1 B1 ;Y2 B2 ;Y3 B3 ;……………… ;Y7 B7 ;Вивід логічного 0 розряд С4 каналу С для дозволу ;перетворення АЦП ;перехід на початок |

|||

|

Назва

|

Кількість тактів, необхідних для виконнаня програми | Число виконань даної програми за один цикл | Кількість тактів, за цикл виконання програми | |||

| Основна програма | 717 | 1 | 717 | |||

| MULL88 | 95 | 3 | 285 | |||

| OP | 108 | 1 | 108 | |||

МЕТА РОБОТИ

Виконання курсової роботи має замету;

• поглиблення теоретичних знань технічних і програмних засобів мікропроцесорних пристроїв (МПП);

• розвиток навиків самостійної розробки загальної структури МПП з аналого-цифровим і цифро-аналоговим перетворенням інформації, побудови принципових схем окремих вузлів пристрою, розробки та відлагодження програмного забезпечення на мові асемблеру мікропроцесора (МП) КР580ВМ;

• набуття навиків роботи з технічною та довідниковою літературою з питань реалізації ряду вузлів МПП, вибору аналого-цифрового і цифро-аналогового перетворювачів (АЦП і ЦАП), використання стандартних підпрограм з прикладного програмного забезпечення МП КР580ВМ80,

Курсова робота повинна сприяти закріпленню і узагальненню знань, отриманих студентом на лекційних і лабораторних заняттях, застосуванню цих знань до комплексного вирішення конкретної інженерної задачі.

Однією з основних вимог до теми курсової роботи є її комплексність, тобто розв'язання взаємно зв'язаних між собою питань. Разом з тим ряд деяких питань теми повинні бути розроблені більш детально на основі загального вирішення задачі.

ЗАВДАННЯ ДО КУРСОВОЇ РОБОТИ

Розробити компоненти технічного і програмного забезпечення мікропроцесорного пристрою, який включає аналогово-цифровий і цифро-аналоговий перетворювачі і виконує функцію лінійної системи автоматизованого регулювання. Системи описується заданим пропорційно-інтегро-диференціальним рівнянням, яке зв'язує аналогові сигнали х (t) на вході і у (t) на виході системи, МПП повинен бути побудований на МП КР580ВМ80. Курсова робота повинна включати такі етапи:

1. Для заданого рівняння систем в регулювання здійснити йoгo часткову дискретизацію і отримати відповідне рівняння цифрового фільтра (ЦФ). Побудувати аналогову схему, яка описується заданим рівнянням.

2. Скласти і детально описати структурну схему МПП з врахуванням особливостей індивідуального завдання.

3. Скласти схему алгоритму функціонування МПП. Вибрати структуру представлення даних при заданій розрядності АЦП, який здійснює дискретизацію і квантування вхідного сигналу.

4. У відповідності з індивідуальним завданням вибрати типи АЦП і ЦАП. Скласти і описати принципові схеми підключення АЦП і ЦАП до МПП. Нарисувати часову діаграму роботи АЦП.

5. Скласти на мові асемблеру мікропроцесора КР580ВМ80 програму вводу інформації через АЦП і виводу через ЦАП.

6. Скласти програму відповідної цифрової обробки інформації. Оцінити верхню

граничну частоту ЦФ. 7. Скласти і детально описати фрагмент принципової схеми реалізації

функціонального вузла, вказаного в індивідуальному завданні. Окремі пункти завдання для курсової роботи за погодженням з викладачем можуть бути уточнені або замінені в процесі виконання роботи.

ВКАЗІВКИ ДО КУРСОВОЇ РОБОТИ

Пояснювальна записка до курсової роботи повинна мати таку структуру.

1. Титульний лист.

2. Завдання до курсової роботи.

3. Зміст.

4. Вступ.

5-n. Основна частина, яка. відповідає пунктам завдання.

n+1. Заключення.

n+2. Список літератури.

Пояснювальна записка повинна бути написана на листах формату All. Рисунки можуть бути нарисовані на міліметровому папері. Принципові схеми повинні бути нарисовані з дотриманням вимог ЄСКД, й схеми алгоритмів - вимог ЄСПД.

При виконанні курсової роботи можна керуватися такими методичними вказівками та інформацією (у відповідності з нумерацією етапів).

1. В лінійних системах автоматичного регулювання вхідний х(t) та вихідний у(t) сигнали в загальному випадку зв'язані пропорційно-інтегро-диференціальним законом регулювання [1]. Прикладом такого рівняння зі всіма трьома типами членів є таке:

де x (t)

- вхідний сигнал,

який і відхиленням

від еталонного

сигналу,

k - коефіцієнт

передачі;

де x (t)

- вхідний сигнал,

який і відхиленням

від еталонного

сигналу,

k - коефіцієнт

передачі;

Т1 і Т2 - сталі часу; у (t) - керуючий сигнал, який подається з системи регулювання на об'єкт керування.

Дискретизація аналогового рівняння полягає в заміні безперервної величний її дискретними відліками (x(t)хn, у(t)yn) і відповідними перетвореннями похідних та

інтегралів. Очевидна дискретизація першої похідної - її заміна першою скінченною різницею:

![]() де

де

![]() t

- інтервал

дискретизації.

t

- інтервал

дискретизації.

Аналогічні скінченні різниці використовуються при дискретизації похідних вищих порядків. Так, наприклад, похідна другого порядку може бути замінена виразом:

![]()

Один зі способів дискретизації інтеграла полягає в його усуненні шляхом диференціювання рівняння Інший спосіб прямої дискретизації зв'язаний з такими перетвореннями:

В результаті часової дискретизації заданого рівняння отримаємо рівняння цифрового фільтра. Це рівняння в загальній формі при обробці інформації в реальному масштабі часу має вигляд:

![]()

де m і k - кількість відліків, які обробляються цифровим фільтром в кожний момент часу (додатні цілі числа); aj, bj - коефіцієнти, які визначають характеристики фільтра.

При наявності в правій частині рівняння членів виду Yn-j фільтр називається

рекурсивним, при відсутності таких членів - нерекурсивним.

Цифровий фільтр може бути реалізований як апаратурно, так і програмно. При апаратурній реалізації необхідними схемними елементами є перемножувачі, суматори і елементи затримки. На рис. 1 зображена структурна схема апаратної реалізації цифрового фільтра, який описується рівнянням:

Yn = a0xn+a1xn-1+b1yn-1+b2yn-2

Рис. Структурна схема реалізації цифрового фільтра;

XY - елемент множення; ВД - елемент затримки; - суматор .

При побудові аналогової схеми, яка відповідає заданому пропорційно-інтегро-диференціальному рівнянню, варіанти рівнянь можна розділити на дві групи. Для варіантів 14-18 вихідний сигнал у (t) заданий явно через вхідний сигнал х (t). його похідні або інтеграл. Такий чином, аналогова схема для цих варіантів буде складатися з суматора, пропорційного елемента, диференціаторів та інтегратора. Кожний з цих елементів може бути побудований на основі операційного підсилювача [6].

На рис. 2 зображена аналогова схема, яка відповідає рівнянню варіант 14. На основі операційного підсилювача ОПІ зібрана схема диференціатора, а на ОП2 - схема додавання-віднімання. Сигнал на виході ОПІ визначається співвідношенням:

z(t)=-R1*![]() *dx(t)/dt

*dx(t)/dt

Рис. 2. Аналогова схема, яка описується заданим рівнянням.