Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по делопроизводству

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Рефераты по косметологии

Рефераты по криминалистике

Рефераты по криминологии

Рефераты по науке и технике

Рефераты по кулинарии

Рефераты по культурологии

Рефераты по зарубежной литературе

Рефераты по логике

Рефераты по логистике

Рефераты по маркетингу

Рефераты по международному публичному праву

Рефераты по международному частному праву

Рефераты по международным отношениям

Рефераты по культуре и искусству

Рефераты по менеджменту

Рефераты по металлургии

Рефераты по муниципальному праву

Рефераты по налогообложению

Рефераты по оккультизму и уфологии

Рефераты по педагогике

Рефераты по политологии

Рефераты по праву

Биографии

Рефераты по предпринимательству

Рефераты по психологии

Рефераты по радиоэлектронике

Рефераты по риторике

Рефераты по социологии

Рефераты по статистике

Рефераты по страхованию

Рефераты по строительству

Рефераты по схемотехнике

Рефераты по таможенной системе

Сочинения по литературе и русскому языку

Рефераты по теории государства и права

Рефераты по теории организации

Рефераты по теплотехнике

Рефераты по технологии

Рефераты по товароведению

Рефераты по транспорту

Рефераты по трудовому праву

Рефераты по туризму

Рефераты по уголовному праву и процессу

Рефераты по управлению

Реферат: Разработка методики программного тестирования цифровых устройств с помощью программного пакета Design Center

Реферат: Разработка методики программного тестирования цифровых устройств с помощью программного пакета Design Center

The abstract

The diploma text contens:

pages –

pictures –

additions –

Key words: testing, model, synchronizing device, demultiplexer, register, counter, gate, D-flip, T-flip.

The aim of this work is developing program testing method for digital devices.

The draughts of the structural electrical schemes of demultiplexer, counter, register and synchronizing device are the add of this work.

Реферат

Пояснительная записка содержит:

страниц –

рисунков –

приложений –

Ключевые слова: тестирование, модель, синхронизирующее устройство,

демультиплексер, регистр, счетчик, вентиль, D-триггер,T-триггер.

Целью данной работы является разработка методики программного тестирования цифровых устройств.

Прилагаются: чертежи структурных электрических схем демультиплексера, вычитающего счетчика, регистра, синхронизирующего устройства.

1 Введение

В настоящее время промышленностью выпускаются интегральные схемы сложные по своей структуре и функциональному предназначению. В сязи с этим возникает проблема контроля выхода годных интегральных схем и выявления причин возникающих неполадок.

Затраты на тестирование сложных интегральных схем с привлечением контрольно-измерительной аппаратуры может во много раз превышать стоимость самой интегральной схемы из-за длительности процесса тестирования и сложности его реализации.

Тестирование на модели разрабатываемой интегральной схемы существенно удешевляет процесс тестирования и сокращает время его осуществления.

На основе проекта интегральных схем, разработанного на этапах логического и топологического проектирования, создаются реальные их образцы . Каждый образец должен затем пройти функциональный контроль, устанавливающий правильность его работы.

В общем случае при тестировании на математической модели или реальном образце обнаруживаются неисправности интегральной схемы путем анализа состояний ее выхода на определенных наборах входных сигналов. Успешное решение задачи тестирования нтегральной схемы на всех стадиях проектирования и изготовления определяет в конечном итоге ее важнейшие характеристики, такие, как бездефектность проектирования, надежность и устойчивость работы, стоимость образцов и другие.

Различают два вида тестирования интегральных схем:

а) функциональное тестирование, осуществляемое на всех этапах разработки логической схемы;

б) функциональный контроль правильности работы образцов интегральных схем после их изготовления.

2 Возможности PSpice как среды моделирования и тестирования

цифровых устройств

Программа PSpice составляет основу системы Design Center, поэтому рассмотрим ее возможности подробнее.

Программа PSpice позволяет проводить следующие виды анализа:

- расчет режима цепи по постоянному току (проводится вначале моделирования перед выполднением других видов анализа без указания специальных деректив;

- многовариантный расчет режима по постоянному току (.DС);

- многовариантный параметричный анализ (.STEP);

- расчет малосигнальных чувствительностей в режиме по постоянному току (.SENS);

- расчет малосигнальных передаточных функций в режиме по постоянному току (.TF);

- расчет частотных характеристик линеаризованной цепи (.AC);

- расчет спектральной плотности внутреннего шума (.NOISE);

- расчет переходных процессов при воздействии сигналов различной формы (.TRAN);

- спектральный анализ (разложение в ряд Фурье результатов расчета переходного процесса) (.FOUR);

- статистический расчет по методу Монте-Карло (.MC);

- расчет на наихудший случай (расчет чувствительности схемы при выбранном виде анализа (.DC, .AC, .TRAN) к параметрам моделей элементов и основанный на этом анализе расчет наихудшего случая по заданному критерию) (.WCASE).

3 Тестирование цифровых устройств на примере

синхронизирующего устройства

3.1 Описание и принцип действия тестируемого устройства

Рассматриваемое синхронизирующее устройство должно под действием комбинации входных сигналов обеспечивать работу в трех режимах:

- режим линии задержки цифровых сигналов;

- режим формирования пачек импульсов цифровых сигналов;

- режим делителя частоты цифровых сигналов.

Число, указывающее количество импульсов, на которое необходимо задержать сигнал, количество импульсов в пачке и число, на которое необходимо разделить частоту сигнала, указывается на входе синхронизирующего устройства.

Для создания модели всего устройства и тестирования его работы, необходимо создать модели функциональных узлов моделируемого устройства.

Моделируемое синхронизирующее устройство можно разбить на четыре фунциональных модуля:

а) управляющая схема. Основная задача этого модуля – подача синхроимпульса на один из функциональных модулей для обеспечения заданного режима работы.

б) линия задержки. Основная задача линии задержки – задержка сигнала на число импульсов определяемое управляющей схемой.

в) формирователь пачек импульсов. Основная задача – формирование пачки импульсов число которых задается управляющей схемой.

г) делитель частоты. Основная задача делителя частоты – формирование сигнала частота которого меньше входного в заданное управляющей схемой число раз.

Таким образом, моделируемое устройство полностью состоит из цифровых компонентов. Это в некоторой степени упрощает создание и тестирование моделей.

Необходимо создать программные модели устройств, протестировать каждую модель, а затем, при положительных результатах тестирований, произвести тестирование всего устройства в целом. При программном тестировании созданных моделей необходимо учитывать возможности используемой вычислительной техники (например при задании шага сигнала).

Для демонстрации преимуществ метода программного тестирования цифровых устройств, можно протестировать синхронизирующее устройство в составе только управляющей схемы и формирователя пачек импульсов.

3.2 Моделирование цифровых компонентов

3.2.1 Общие сведения

Моделирование может осуществляться с помощью библиотек логических примитивов созданных самим разработчиком или с помощью библиотек встроенных в программу PSpice.

Рассмотрим первый способ.

Любое цифровое устройство разрабатывается на основе элементной базы. Элементная база выбирается из требований к электрическим параметрам устройства. В данной работе в качестве примера выбрана элементная база на основе КМОП-лигики. Рассматриваемая в данной работе цифровая схема представляет собой синхронизирующее устройство, логический базис которого реализован на КМОП-логики.

В настоящее время широкое применение КМОП-схем обусловлено их минимальным энергопотреблением, повышенной помехоустойчивостью, воз-

OUTLD - выходная емкость в фарадах (по умолчанию 0);

DRVH - выходное сопротивление высокого уровня в омах (по умолчанию

50 Oм);

DRVL - выходное сопротивление низкого уровня в омах (по умолчанию

50 Ом);

Так как в данной работе необходимо протестировать только правильность работы моделируемого устройства,без контроля параметров его элемнетной базы из которой он составлен, то необходимо выбрать второй способ моделирования.

3.2.2 Модели источников логических сигналов

При моделировании цифровых устройств используются модели постоянных источников логических сигналов и модели генераторов входных логических сигналов.

Модель источника постоянного логического сигнала описывается следующим образом:

U ()

+ >

+

Для моделей цифровых устройств с определенной элементной базой узлы питания могут описываться определенными операторами в теле модели источника. Для моделей с элементной базой на КМОП-логике узлы питания описываются следующим образом:

- узел питания “+” – $ g_cd4000_vdd;

- узел питания “-“ – $ g_cd4000_vss;

Модель генератора входных логических сигналов описывается следующим образом:

В цифровом синхронизирующем устройстве, рассматриваемом в данной работе, используются только вентили с двумя состояниями. Рассмотрим модели используемых в работе вентилей.

Модель с двумя состояниями имеет следующий вид:

U [(параметры)]

+

+

+ .

Форма описания модели динамики:

.model ugate[(параметры модели)].

В системе Design Center вентили представлены в двух видах: одиночные вентили и сборки(массивы) вентилей.Одиночный вентиль имеет один или несколько входов и один выход.Сборки вентилей состоят из одного или более одинаковых вентилей.Использование сборок позволяет работать непосредственно со стандартными элементами интегральных схем, имеющими часто в одном корпусе несколько вентилей.

В соответствии с рисунком Б.1 приложения Б в данной работе используются следующие модели вентилей:

INV- инвертор;

INVA - сборка инверторов;

AND - вентиль “И”;

ANDA - сборка вентилей “И”;

NAND - вентиль “И-НЕ”;

NANDA- сборка вентилей “И-НЕ”;

OR- вентиль “ИЛИ”;

NOR - вентиль “ИЛИ-НЕ”;

NORA - сборка вентилей “ИЛИ-НЕ ”;

.model source uio(drvh=50 drvl=50)

.probe

.tran 10ns 400ns

.end

Результат тестирования регистра приведен в приложении В.

Электрическая структурная схема регистра RG1 приведена в комплекте чертежей.

Регистр является регистром с паралельным приемом и выдачей информации. Изменение хранящейся информации происходит после изменения сигналов на входах 01 и 02.

3.2.6 Формирование модели управляющей схемы, входящей в состав цифрового синхронизирующего устройства. Тестирование модели

управляющей схемы

Рассмотренные ранее модели цифровых устройств комбинационного и последовательностного типа позволяют построить модель одного из функциональных узлов тестируемого в данной работе синхронизирующего устройства и протестировать его функционирование. Функционируемой и тестируемой на данном этапе моделью функционального узла является управляющая схема. Ее задачей является перенос синхронизирующего сигнала со входа 06 на один из выходов демультиплексера, при соответствующих сигналах на входах 01 и 02 регистра RG1 и запись двоичного числа в счетчик СТ1. Последнее необходимо для задания числа импульсов на выходе формирователя пачек импульсов.

Ниже приведена модель управляющей схемы и результат ее тестирования:

u1 inva(2) up um 09 10 out1a out2a delay1 in_out

u2 anda(3,3) up um 10 03 out1a 09 out2a 03 03 09 10 4 5

+6 delay1 in_out

.model delay1 ugate

u3 dff(2) up um 04 05 03 01 02 07 08 09 10 delay source

Ugnr1 STIM (1,1)

+ up um

+03

+ source TIMESTEP = 10.00000E-9 IO_LEVEL=0

+ 0.000000C 0

+ LABEL = again

+ 1.000000C 1

+ 2.000000C 0

+ 3.000000C GOTO again -1 TIMES

uconst1 pullup(2) $g_cd4000_vdd $g_cd4000_vss 04 01 in_out

uconst0 pulldn(1) $g_cd4000_vdd $g_cd4000_vss 02 in_out

ur STIM (1,1)

+ $G_DPWR $G_DGND 05 source TIMESTEP = 1.000000E-9 IO_LEVEL=0

+ 0.000000s 0

+ 2.000000E-9s 1

* uconst0 pulldn(1) $g_cd4000_vdd $g_cd4000_vss S in_out

.model delay ueff

.model in_out uio(drvh=1e4 drvl=1e4)

.options digmntymx=2

.model source uio(drvh=50 drvl=50)

.probe

.tran 10ns 400ns

.end

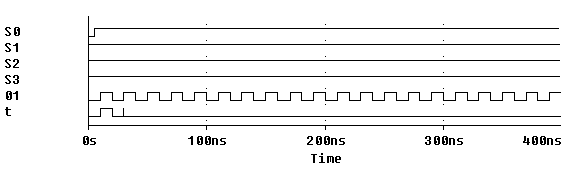

Результат тестирования управляющей схемы приведен в приложении Г.

3.2.7 Создание модели формирователя пачек импульсов, входящего в состав цифрового синхронизирующего устройства. Тестирование модели формирователя пачек импульсов.

Основной задачей формирователя пачек импульсов является форми-рование сигнала в состав которого входят импульсы, число которых задается управляющей схемой.

В основе формирователя пачек импульсов лежит вычитающий счетчик СТ1, построенный на Т-триггерах.

В библиотеке PSpice нет модели Т-триггера, так как данный тип триггера может быть реализован на основе D-триггера. Данная реализация производится путем соединения инвертирующего выхода D-триггера с его D-входом. Таким образом получается триггер с одним входом и состояние триггера меняется с уровнем сигнала на его входе.

Ниже приведена модель Т-триггера:

u1 dff(1) up um R S c inv out inv delay source

Ugnr1 STIM (1,1) up um c source TIMESTEP = 10.00000E-9 IO_LEVEL=0

+ 0.000000C 0

+ LABEL = again

+ 1.000000C 1

+ 2.000000C 0

+ 3.000000C GOTO again -1 TIMES

uconst1 pullup(1) $g_cd4000_vdd $g_cd4000_vss S source

ur STIM (1,1) $G_DPWR $G_DGND R sour TIMESTEP = 1.E IO_LEVEL=0

+ 0.000000s 0

+ 2.000000E-9s 1

.model delay ueff

.options digmntymx=2

.model source uio(drvh=50 drvl=50)

.probe

.tran 10ns 400ns

.end

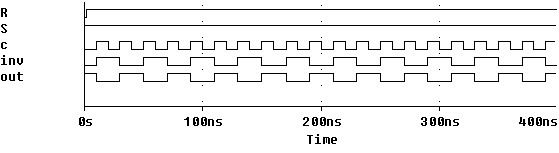

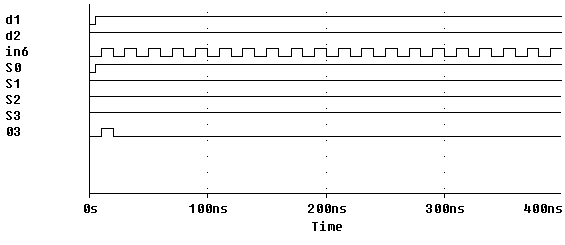

Результат тестирования Т-триггера приведен в приложении Г.

.model dinamics ueff

.model dinam ugate

.tran 10ns 400ns

.probe

.end

Результат тестирования работы формирователя пачек импульсов приведен в приложениии Д.

3.2.8 Объединение моделей функциональных узлов и тестирование

работы всей модели синхронизирующего устройства

Тестирование всей модели синхронизирующего устройства можно осуществить двумя способами.

Первый способ заключается в непосредственном соединении всех разработанных моделей, входящих в устройство и представить модель устройства ввиде одной программы.

Второй способ заключается в создании библиотечных файлов таких логических элементов, как регистр, демультиплексер и счетчик. При составлении модели, в теле основной программы необходимо вставить операторы вызывающие нужные библиотечные файлы.

Первый способ необходим при создании и тестировании моделей несложных устройств, в которых модели различных логических элементов используются не чаще одного раза.

Второй способ позволяет избежать громоздких описаний моделей сложных устройств, в которые входит большое количество одинаковых элементов.

В данной работе удобнее использовать первый способ.

Программная модель синхронизирующего устройства приведена ниже.

Приложение Б

Виды используемых в работе вентилей и тестирование работы

демультиплексера

1

&

&

INV AND NAND

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

1

1

OR NOR

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Рисунок Б.1 – Стандартные вентили используемые в данной работе

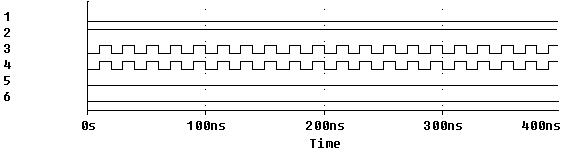

Рисунок Б.2 – Результат тестирования модели демультиплексера

Приложение В

Результат тестирования регистра и пример триггеров с динамическим

управлением

JKFF DFF

S T

D

C

R

S T

J

K

C

R

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

S T

D

C

R

S T

J

K

C

R

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

а) б)

а – JK - триггер;

б – D - триггер;

Рисунок В.1 – Триггеры с динамическим управлением.

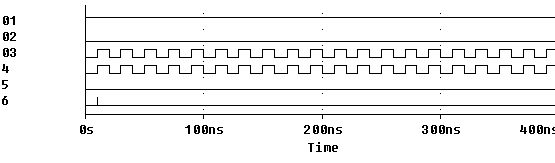

Рисунок В.2 – Тестирование работы регистра.

Приложение Г

Результаты тестирования управляющей схемы и Т-триггера

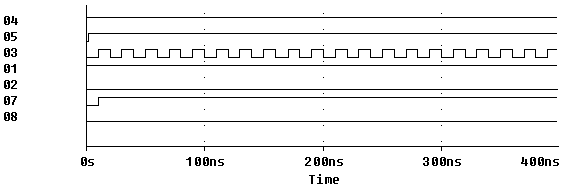

Рисунок Г.1 – Тестирование управляющей схемы.

Рисунок Г.2 – Тестирование Т-триггера.

Приложение Д

Результат тестирования формирователя пачек импульсов и всего

синхронизирующего устройства

Рисунок Д.1 – Тестирование формирователя пачек импульсов.

Рисунок Д.2 – Результат тестирования синхронизирующего устройства.

Министерство общего и профессионального образования Российской Федерации

Новгородский государственный университет

имени Ярослава Мудрого

_________________________________________________________________________

Кафедра физики твёрдого тела и микроэлектроники

|

УТВЕРЖДАЮ |

|

Зав. кафедрой ФТТМ |

|

_________ Б.И.Селезнёв |

|

“_____” __________1999 г. |

Задание на выпускную работу

на получение академической степени бакалавра техники и технологий

Студенту группы 5031 Хаимову Даниилу Исхаковичу

Тема работы: Разработка методики программного тестирования цифровых

устройств с помощью программного пакета Design Center

(утверждена на заседании кафедры "_____" __________ 1999 г.)

2 Срок сдачи законченной работы: 22.06.99 г.

3 Исходные данные к работе:

4 Содержание пояснительной записки (перечень подлежащих разработке вопросов):

5 Перечень графического материала:

6 Прочие условия:

7 Консультанты по работе (с указанием относящихся к ним разделов работы):

Сапожников А.А. (норм контроль)

![]()

|

Задание выдал (руководитель) |

Задание принял к исполнению |

|

Д. т. н., профессор |

студент группы 5031 |

|

__________ Селезнёв Б.И. |

__________ Хаимов Д.И. |

|

"_____" __________ 1999 г. |

"_____" __________ 1999 г. |

Новгород Великий

1999